|

|

PDF ST-PLC-AFE Data sheet ( Hoja de datos )

| Número de pieza | ST-PLC-AFE | |

| Descripción | analog front-end | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ST-PLC-AFE (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ST-PLC-AFE

Power-line communication, analog front-end

Features

• Integrated, analog power-line driver and

receiver

• EN 50065-1 - CENELEC, European bands A,

B, C, and D

• Supports FSK, S-FSK, and OFDM

• Supports PRIME, G3, and IEC 61334

• Half-duplex mode

• Thermal protection

• Programmable overcurrent protection

• 10 V p-p single-ended output range

• 20 V p-p differential-ended output range

• Programmable transmitter chain (Tx) and

receiver chain (Rx) filters

• Programmable Rx and Tx gain control

• 7 V to 14 V line driver supply

• Low power consumption: 10 mW (receive

mode)

• Reverse sensitivity 20 µVrms typical

• Four-wire, serial peripheral interface

• Two integrated zero cross detectors

• Temperature range: -40 °C to 125 °C

Datasheet - production data

Applications

• E-metering

• Smart grid applications

• Smart light control

• Solar energy management

• Building automation

• Remote monitoring and control

Description

The ST-PLC-AFE is a power-line communication,

analog front-end device capable of capacitive or

transformer-coupled connections to the power

line while under the control of a microcontroller or

a DSP.

The line driver is able to drive low-impedance

lines, requiring up to 1.65 A, into reactive loads. It

can also work in differential mode for high

performance, as well as single-ended mode for a

low-cost bill of materials (BOM). The integrated

receiver is able to detect signals down to 20

µVrms. The system works in half-duplex mode.

The AFE is protected against over temperature

and short-circuit conditions. It also provides four

adjustable current limits through an internal

register. Through the four-wire serial peripheral

interface, or SPI, each functional block can be

enabled or disabled to optimize power

consumption.

February 2016

This is information on a product in full production.

DocID028727 Rev 1

1/58

www.st.com

1 page

ST-PLC-AFE

Package pin description and connections

Table 1. QFN48 pin description (continued)

Pin no.

Name

Type

Description

31 PA_GND

32 PA_GND

POWER PA

Power amplifier ground

33 PA_OUTP

34 PA_OUTP

OUT PA

PA output non inverting side

35 PA_VDD

36 PA_VDD

POWER PA

Power amplifier positive supply

37 NC5

NC

Not connected to the Silicon

38 RX_INP

39 RX_INN

IN ANALOG

Rx chain input pin, non-inverting input

Rx chain input pin, inverting input

40 RX_FOUTN

41 RX_FOUTP

OUT ANALOG

Rx output after LPF filter, inverting output

Rx output after LPF filter, non-inverting output

42 AVDD

43 AGND

Analog positive supply

POWER ANALOG

Analog ground

44 RX_PGA2_INP

IN ANALOG

45 RX_PGA2_INN

Rx PGA2 input pin, non-inverting input

Rx PGA2 input pin, inverting input

46 RX PGA2_OUT

OUT ANALOG

47 ZC2_OUT

Rx PGA2 output pin, single mode

Zero cross detector 2 output node

48 ZC2_IN

IN ANALOG

Zero cross detector 2 input node

DocID028727 Rev 1

5/58

58

5 Page

ST-PLC-AFE

General description

2.2

2.2.1

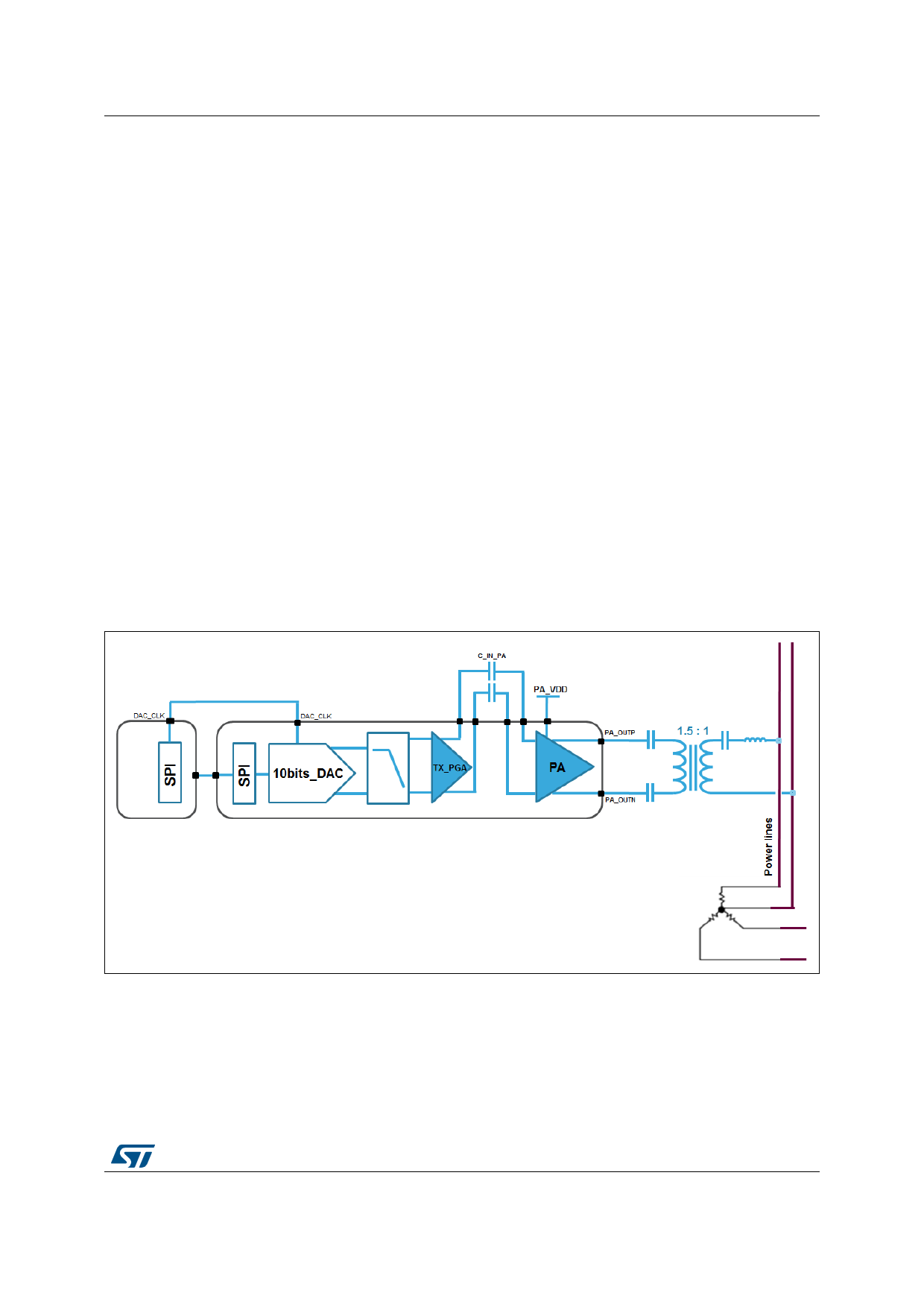

Tx block

The Tx block is divided into an internal DAC, an internal fourth-order filter, a programmable

amplifier, and a power liner driver. There are two ways to drive this transmission line:

1. The internal DAC driving mode, achieved through the SPI interface and the internal

10-bit DAC.

2. Using an external driving mode where the signal received by the ST-PLC-AFE is purely

analog, coming from an external MCU DAC. This signal is applied on the TX_INP input

pin.

Tx PGA can be configured through the SPI to operate as an attenuator or to work in

follower. The gain steps of the Tx PGA are 6 dB, 0 dB, -18 dB, and -36 dB. The gain can be

programmed through the TX_PGA1<1:0> bits in the Gain register.

The Tx_filter is a unity-gain, fourth-order, low-pass filter. Its cutoff frequency is selectable

between CENELEC A or CENELEC B, C, or D modes. The selection of the band is

achieved through the BAND_SEL bit in the Enable register.

Internal DAC driving mode

The ST-PLC-AFE accepts serial data from the microprocessor and writes the data to the

internal DAC registers. Operating in DAC mode results in the lowest distortion signal

injected onto the AC mains. DAC mode is selected by setting the DAC_EN bit in the Enable

register to 1. Figure 5 and Figure 6 show the connection to the power line while using the

internal DAC in differential mode and in single-ended mode respectively.

Figure 5. Connection to the power line in differential mode

DocID028727 Rev 1

11/58

58

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ST-PLC-AFE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ST-PLC-AFE | analog front-end | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |