|

|

PDF F59D4G81A Data sheet ( Hoja de datos )

| Número de pieza | F59D4G81A | |

| Descripción | 4 Gbit (512M x 8 / 256M x 16) 1.8V NAND Flash Memory | |

| Fabricantes | Elite Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de F59D4G81A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ESMT

Flash

FEATURES

Voltage Supply: 1.8V (1.7V ~ 1.95V)

Organization

x8:

- Memory Cell Array: (512M + 8M) x 8bit

- Data Register: (2K + 64) x 8bit

x16:

- Memory Cell Array: (256M + 4M) x 16bit

- Data Register: (1K + 32) x 16bit

Automatic Program and Erase

x8:

- Page Program: (2K + 64) Byte

- Block Erase: (128K + 4K) Byte

x16:

- Page Program: (1K + 32) Word

- Block Erase: (64K + 2K) Word

Page Read Operation

- Page Size: (2K + 64) Byte (x8)

Page Size: (1K + 32) Word (x16)

- Random Read: 25us (Max.)

- Serial Access: 45ns (Min.)

Memory Cell: 1bit/Memory Cell

Fast Write Cycle Time

- Program time: 350us (Typ.)

- Block Erase time: 3.5ms (Typ.)

F59D4G81A / F59D4G161A

4 Gbit (512M x 8 / 256M x 16)

1.8V NAND Flash Memory

Command/Address/Data Multiplexed I/O Port

Hardware Data Protection

- Program/Erase Lockout During Power Transitions

Reliable CMOS Floating Gate Technology

- ECC Requirement: x8 - 4bit/512Byte

x16 - 4bit/256Word

- Endurance: 100K Program/Erase cycles

- Data Retention: 10 years

Command Register Operation

Automatic Page 0 Read at Power-Up Option

- Boot from NAND support

- Automatic Memory Download

NOP: 4 cycles

Cache Program/Read Operation

Copy-Back Operation

Two-Plane Operation

EDO mode

Bad-Block-Protect

ORDERING INFORMATION

Product ID

Speed

Package

x8:

F59D4G81A -45TG

45 ns

48 pin TSOPI

x16:

F59D4G161A -45TG 45 ns

48 pin TSOPI

Comments

Pb-free

Pb-free

GENERAL DESCRIPTION

The device is a 512Mx8bit with spare 16Mx8bit capacity (or

256Mx16bit with spare 8Mx16bit capacity). The device is offered

in 1.8V VCC Power Supply. Its NAND cell provides the most

cost-effective solution for the solid state mass storage market.

The memory is divided into blocks that can be erased

independently so it is possible to preserve valid data while old

data is erased.

The device contains 4096 blocks, composed by 64 pages

consisting in two NAND structures of 32 series connected Flash

cells. A program operation allows to write the 1056-Word page in

typical 350us and an erase operation can be performed in typical

3.5ms on a 128K-Byte for X8 device block (or 64K-Word for X16

device block).

Data in the page mode can be read out at 45ns cycle time per

Elite Semiconductor Memory Technology Inc.

Word. The I/O pins serve as the ports for address and command

inputs as well as data input/output. The copy back function

allows the optimization of defective blocks management: when a

page program operation fails the data can be directly

programmed in another page inside the same array section

without the time consuming serial data insertion phase. The

cache program feature allows the data insertion in the cache

register while the data register is copied into the Flash array.

This pipelined program operation improves the program

throughput when long files are written inside the memory. A

cache read feature is also implemented. This feature allows to

dramatically improving the read throughput when consecutive

pages have to be streamed out. This device includes extra

feature: Automatic Read at Power Up.

Publication Date: May 2014

Revision: 1.4

1/54

1 page

ESMT

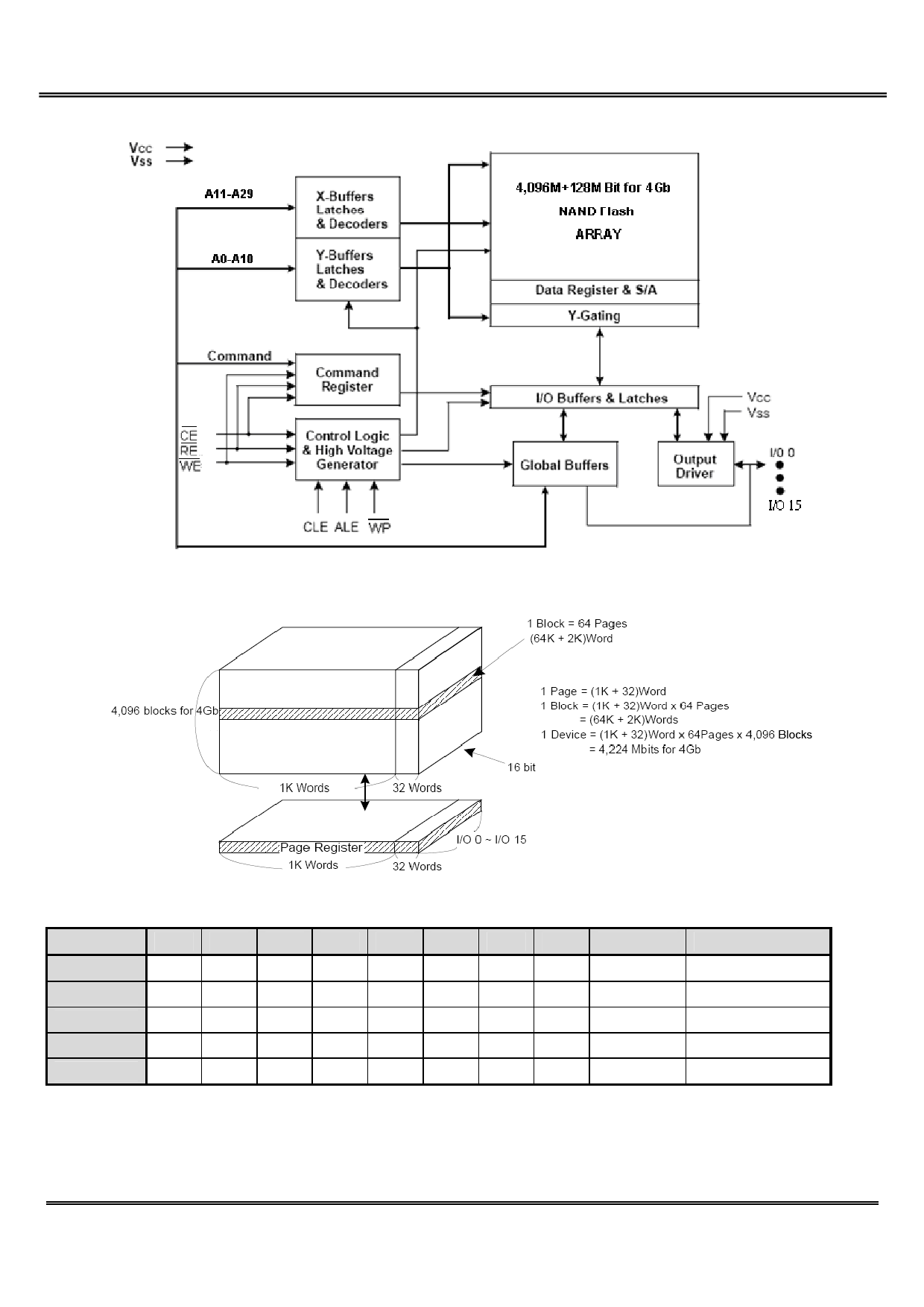

BLOCK DIAGRAM (x16)

F59D4G81A / F59D4G161A

ARRAY ORGANIZATION (x16)

Array Address (x16)

I/O0 I/O1 I/O2 I/O3 I/O4 I/O5 I/O6 I/O7 I/O8~I/O15

Address

1st cycle A0 A1 A2 A3 A4 A5 A6 A7

L* Column Address

2nd cycle A8 A9 A10 L* L* L* L* L*

L* Column Address

3rd cycle

A11 A12 A13 A14 A15 A16 A17 A18

L*

Row Address

4th cycle

5th cycle

A19 A20 A21 A22 A23 A24 A25 A26

A27 A28

L*

L*

L*

L*

L*

L*

L*

L*

Row Address

Row Address

NOTE:

Column Address: Starting Address of the Register.

* L must be set to “Low”.

* The device ignores any additional input of address cycles than required.

A17 is for Plane Address setting.

Elite Semiconductor Memory Technology Inc.

Publication Date: May 2014

Revision: 1.4

5/54

5 Page

ESMT

F59D4G81A / F59D4G161A

NAND Flash Technical Notes

Mask Out Initial Invalid Block(s)

Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed by ESMT. The

information regarding the initial invalid block(s) is called the initial invalid block information. Devices with initial invalid block(s) have the

same quality level as devices with all valid blocks and have the same AC and DC characteristics. An initial invalid block(s) does not

affect the performance of valid block(s) because it is isolated from the bit line and the common source line by a select transistor. The

system design must be able to mask out the initial invalid block(s) via address mapping.

The 1st block, which is placed on 00h block address, is guaranteed to be a valid block up to 1K program/erase cycles with 4bit/512Byte

(4bit/256Word) ECC.

Identifying Initial Invalid Block(s) and Block Replacement Management

All device locations are erased (FFh) except locations where the initial invalid block(s) information is written prior to shipping. The initial

invalid block(s) status is defined by the 1st byte in the spare area. ESMT makes sure that either the 1st or 2nd page of every initial

invalid block has non-FFh data at the 1st byte column address in the spare area.

Do not erase or program factory-marked bad blocks. The host controller must be able to recognize the initial invalid block information

and to create a corresponding table to manage block replacement upon erase or program error when additional invalid blocks develop

with Flash memory usage.

Elite Semiconductor Memory Technology Inc.

Publication Date: May 2014

Revision: 1.4

11/54

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet F59D4G81A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| F59D4G81A | 4 Gbit (512M x 8 / 256M x 16) 1.8V NAND Flash Memory | Elite Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |