|

|

PDF AX1000 Data sheet ( Hoja de datos )

| Número de pieza | AX1000 | |

| Descripción | Axcelerator Family FPGAs | |

| Fabricantes | Actel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AX1000 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Axcelerator Family FPGAs

v2.7

™

ue

Leading-Edge Performance

• 350+ MHz System Performance

• 500+ MHz Internal Performance

• High-Performance Embedded FIFOs

• 700 Mb/s LVDS Capable I/Os

Specifications

• Up to 2 Million Equivalent System Gates

• Up to 684 I/Os

• Up to 10,752 Dedicated Flip-Flops

• Up to 295 kbits Embedded SRAM/FIFO

• Manufactured on Advanced 0.15 μm CMOS Antifuse

Process Technology, 7 Layers of Metal

Features

• Single-Chip, Nonvolatile Solution

• Up to 100% Resource Utilization with 100% Pin Locking

• 1.5V Core Voltage for Low Power

• Footprint Compatible Packaging

• Flexible, Multi-Standard I/Os:

– 1.5V, 1.8V, 2.5V, 3.3V Mixed Voltage Operation

– Bank-Selectable I/Os – 8 Banks per Chip

– Single-Ended I/O Standards: LVTTL, LVCMOS, 3.3V

PCI, and 3.3V PCI-X

– Differential I/O Standards: LVPECL and LVDS

Table 1-1 • Axcelerator Family Product Profile

Device

Capacity (in Equivalent System Gates)

Typical Gates

Modules

Register (R-cells)

Combinatorial (C-cells)

Maximum Flip-Flops

Embedded RAM/FIFO

Number of Core RAM Blocks

Total Bits of Core RAM

Clocks (Segmentable)

Hardwired

Routed

PLLs

I/Os

I/O Banks

Maximum User I/Os

Maximum LVDS Channels

Total I/O Registers

Package

CSP

PQFP

BGA

FBGA

CQFP

CCGA

AX125

125,000

82,000

672

1,344

1,344

4

18,432

4

4

8

8

168

84

504

180

256, 324

– Voltage-Referenced I/O Standards: GTL+, HSTL

Class 1, SSTL2 Class 1 and 2, SSTL3 Class 1 and 2

– Registered I/Os

– Hot-Swap Compliant I/Os (except PCI)

– Programmable Slew Rate and Drive Strength on

Outputs

– Programmable Delay and Weak Pull-Up/Pull-Down

Circuits on Inputs

• Embedded Memory:

– Variable-Aspect 4,608-bit RAM Blocks (x1, x2, x4,

x9, x18, x36 Organizations Available)

– Independent, Width-Configurable Read and Write Ports

– Programmable Embedded FIFO Control Logic

• Segmentable Clock Resources

• Embedded Phase-Locked Loop:

– 14-200 MHz Input Range

– Frequency Synthesis Capabilities up to 1 GHz

• Deterministic, User-Controllable Timing

• Unique In-System Diagnostic and Debug Capability

with Actel Silicon Explorer II

• Boundary-Scan Testing Compliant with IEEE Standard

1149.1 (JTAG)

• FuseLockTM Secure Programming Technology

Prevents Reverse Engineering and Design Theft

AX250

250,000

154,000

1,408

2,816

2,816

12

55,296

4

4

8

8

248

124

744

208

256, 484

208, 352

AX500

500,000

286,000

2,688

5,376

5,376

16

73,728

4

4

8

8

336

168

1,008

AX1000

1,000,000

612,000

6,048

12,096

12,096

36

165,888

4

4

8

8

516

258

1,548

AX2000

2,000,000

1,060,000

10,752

21,504

21,504

64

294,912

4

4

8

8

684

342

2,052

208

484, 676

208, 352

729

484, 676, 896

352

624

896, 1152

352

624

November 2008

© 2008 Actel Corporation

i

*See Actel’s website for the latest version of the datasheet.

http://www.Datasheet4U.com

1 page

Table of Contents

Axcelerator Family FPGAs

1152-Pin FBGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-67

208-Pin PQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-78

208-Pin CQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-83

352-Pin CQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-88

624-Pin CCGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-102

Datasheet Information

List of Changes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

Datasheet Categories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

Export Administration Regulations (EAR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-5

v2.7

v

http://www.Datasheet4U.com

5 Page

Axcelerator Family FPGAs

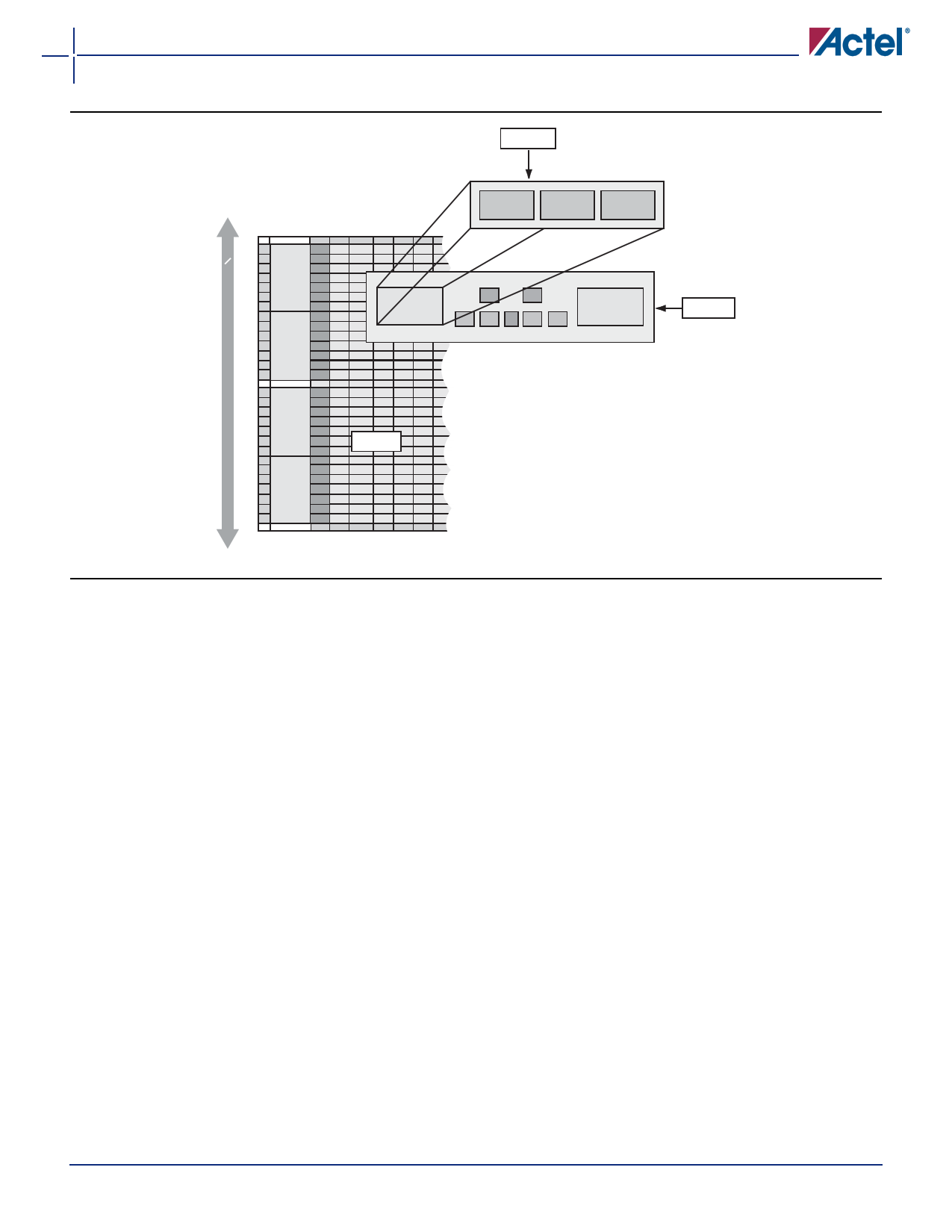

I/O Module

I

O

4k

RAM/

B FIFO

A

N

K 4k

RAM/

FIFO

4k

RAM/

FIFO

4k

RAM/

FIFO

InReg OutReg EnReg

I/O

Module

TX TX

RX RX B RX RX

I/O

Module

I/O Cluster

CoreTile

Figure 1-7 • I/O Cluster Arrangement

Routing

The AX hierarchical routing structure ties the logic

modules, the embedded memory blocks, and the I/O

modules together (Figure 1-8 on page 1-6). At the lowest

level, in and between SuperClusters, there are three local

routing structures: FastConnect, DirectConnect, and

CarryConnect routing. DirectConnects provide the highest

performance routing inside the SuperClusters by

connecting a C-cell to the adjacent R-cell. DirectConnects

do not require an antifuse to make the connection and

achieve a signal propagation time of less than 0.1 ns.

FastConnects provide high-performance, horizontal

routing inside the SuperCluster and vertical routing to

the SuperCluster immediately below it. Only one

programmable connection is used in a FastConnect path,

delivering a maximum routing delay of 0.4 ns.

CarryConnects are used for routing carry logic between

adjacent SuperClusters. They connect the FCO output of

one two-bit, C-cell carry logic to the FCI input of the two-

bit, C-cell carry logic of the SuperCluster below it.

CarryConnects do not require an antifuse to make the

connection and achieve a signal propagation time of less

than 0.1 ns.

The next level contains the core tile routing. Over the

SuperClusters within a core tile, both vertical and

horizontal tracks run across rows or columns,

respectively. At the chip level, vertical and horizontal

tracks extend across the full length of the device, both

north-to-south and east-to-west. These tracks are

composed of highway routing that extend the entire

length of the device (segmented at core tile boundaries)

as well as segmented routing of varying lengths.

Global Resources

Each family member has three types of global signals

available to the designer: HCLK, CLK, and GCLR/GPSET.

There are four hardwired clocks (HCLK) per device that

can directly drive the clock input of each R-cell. Each of

the four routed clocks (CLK) can drive the clock, clear,

preset, or enable pin of an R-cell or any input of a C-cell

(Figure 1-3 on page 1-3).

Global clear (GCLR) and global preset (GPSET) drive the

clear and preset inputs of each R-cell as well as each I/O

Register on a chip-wide basis at power-up.

Each HCLK and CLK has an associated analog PLL (a total

of eight per chip). Each embedded PLL can be used for

clock delay minimization, clock delay adjustment, or

clock frequency synthesis. The PLL is capable of

v2.7

1-5

http://www.Datasheet4U.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AX1000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AX1000 | Axcelerator Family FPGAs | Actel |

| AX1006 | 400mA Low Dropout Linear Regulator | AXElite |

| AX1006 | Audio Player Microcontroller | AppoTech |

| AX1007 | 1A Low Dropout Linear Regulator | AXElite |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |