|

|

PDF ADF4150HV Data sheet ( Hoja de datos )

| Número de pieza | ADF4150HV | |

| Descripción | Fractional-N/Integer-N PLL Synthesizer | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADF4150HV (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

High Voltage, Fractional-N/

Integer-N PLL Synthesizer

ADF4150HV

FEATURES

Fractional-N synthesizer and integer-N synthesizer

High voltage charge pump: VP = 6 V to 30 V

Tuning range: 1.0 V to 29 V (or ±1 V from VP supply rails)

RF bandwidth to 3.0 GHz

Programmable divide-by-1/-2/-4/-8/-16 outputs

Synthesizer power supply: 3.0 V to 3.6 V

Programmable dual-modulus prescaler of 4/5 or 8/9

Programmable output power level

Programmable charge pump currents

RF output mute function

3-wire serial interface

Analog and digital lock detect

APPLICATIONS

Wireless infrastructure

Microwave point-to-point/point-to-multipoint radios

VSAT radios

Test equipment

Private land mobile radios

GENERAL DESCRIPTION

The ADF4150HV is a 3.0 GHz, fractional-N or integer-N

frequency synthesizer with an integrated high voltage charge

pump. The synthesizer can be used to drive external wideband

VCOs directly, eliminating the need for operational amplifiers

to achieve higher tuning voltages. This simplifies design and

reduces cost while improving phase noise, in contrast to active

filter topologies, which tend to degrade phase noise compared

to passive filter topologies.

The VCO frequency can be divided by 1, 2, 4, 8, or 16 to allow

the user to generate RF output frequencies as low as 31.25 MHz.

For applications that require isolation, the RF output stage can be

muted. The mute function is both pin- and software-controllable.

A simple 3-wire interface controls all on-chip registers. The

charge pump operates from a power supply ranging from 6 V to

30 V, whereas the rest of the device operates from 3.0 V to 3.6 V.

The ADF4150HV can be powered down when not in use.

SDVDD

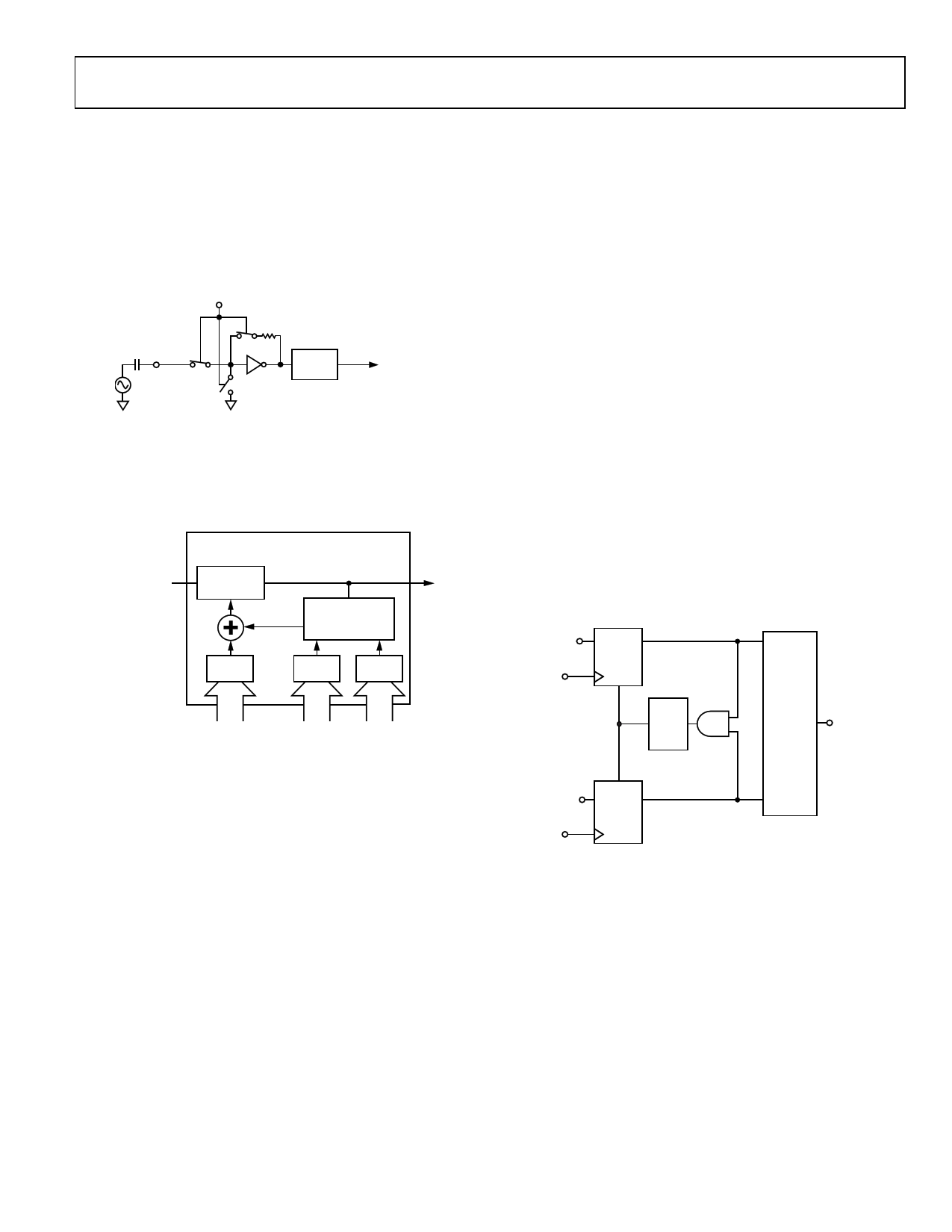

FUNCTIONAL BLOCK DIAGRAM

AVDD

DVDD

VP

RSET

REFIN

CLK

DATA

LE

×2

DOUBLER

10-BIT R

COUNTER

÷2

DIVIDER

DATA REGISTER

FUNCTION

LATCH

INTEGER FRACTION MODULUS

VALUE

VALUE

VALUE

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

N COUNTER

LOCK

DETECT

MULTIPLEXER

HIGH VOLTAGE

CHARGE

PUMP

PHASE

COMPARATOR

CURRENT

SETTING

DIVIDE-BY-1/

-2/-4/-8/-16

MULTIPLEXER

MUXOUT

LD

BOOST

MODE

OUTPUT

STAGE

RF

INPUT

CPOUT

RFOUT+

RFOUT–

PDBRF

RFIN+

RFIN–

CE

Figure 1.

GND

CPGND SDGND

ADF4150HV

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2011 Analog Devices, Inc. All rights reserved.

Free Datasheet http://www.datasheet4u.com/

1 page

ADF4150HV

TIMING CHARACTERISTICS

AVDD = DVDD = SDVDD = 3.3 V ± 10%; VP = 6.0 V to 30 V; GND = 0 V; TA = TMIN to TMAX, unless otherwise noted. Operating temperature

range is −40°C to +85°C.

Table 2.

Parameter

t1

t2

t3

t4

t5

t6

t7

Limit

20

10

10

25

25

10

20

Unit

ns min

ns min

ns min

ns min

ns min

ns min

ns min

Description

LE setup time

DATA to CLK setup time

DATA to CLK hold time

CLK high duration

CLK low duration

CLK to LE setup time

LE pulse width

Timing Diagram

CLK

DATA

DB31 (MSB)

LE

t1

LE

t4 t5

t2 t3

DB30

DB2

(CONTROL BIT C3)

DB1

(CONTROL BIT C2)

Figure 2. Timing Diagram

DB0 (LSB)

(CONTROL BIT C1)

t7

t6

Rev. 0 | Page 5 of 28

Free Datasheet http://www.datasheet4u.com/

5 Page

CIRCUIT DESCRIPTION

REFERENCE INPUT SECTION

The reference input stage is shown in Figure 14. The SW1 and

SW2 switches are normally closed. The SW3 switch is normally

open. When power-down is initiated, SW3 is closed, and SW1

and SW2 are opened. In this way, no loading of the REFIN pin

occurs during power-down.

POWER-DOWN

CONTROL

NC 100kΩ

REFIN NC

SW2

SW1

SW3

NO

TO R COUNTER

BUFFER

Figure 14. Reference Input Stage

RF N DIVIDER

The RF N divider allows a division ratio in the PLL feedback

path. The division ratio is determined by the INT, FRAC, and

MOD values, which build up this divider (see Figure 15).

FROM

VCO OUTPUT/

OUTPUT DIVIDERS

RF N DIVIDER

N COUNTER

N = INT + FRAC/MOD

TO PFD

THIRD-ORDER

FRACTIONAL

INTERPOLATOR

INT

VALUE

MOD

VALUE

FRAC

VALUE

Figure 15. RF N Divider

INT, FRAC, MOD, and R Counter Relationship

The INT, FRAC, and MOD values, in conjunction with the

R counter, make it possible to generate output frequencies that

are spaced by fractions of the PFD frequency. For more informa-

tion, see the RF Synthesizer—A Worked Example section.

The RF VCO frequency (RFOUT) equation is

RFOUT = (fPFD/RF Divider) × [INT + (FRAC/MOD)]

(1)

where:

RFOUT is the output frequency of the external voltage controlled

oscillator (VCO).

RF Divider is the output divider that divides down the VCO

frequency.

INT is the preset divide ratio of the binary 16-bit counter (23 to

32,767 for the 4/5 prescaler, 75 to 65,535 for the 8/9 prescaler).

FRAC is the numerator of the fractional division (0 to MOD − 1).

MOD is the preset fractional modulus (2 to 4095).

ADF4150HV

The PFD frequency (fPFD) equation is

fPFD = REFIN × [(1 + D)/(R × (1 + T))]

(2)

where:

REFIN is the reference input frequency.

D is the REFIN doubler bit.

R is the preset divide ratio of the binary 10-bit programmable

reference counter (1 to 1023).

T is the REFIN divide-by-2 bit (0 or 1).

Integer-N Mode

If FRAC = 0 and the DB8 (LDF) bit in Register 2 is set to 1,

the synthesizer operates in integer-N mode. The DB8 bit in

Register 2 should be set to 1 for integer-N digital lock detect.

R Counter

The 10-bit R counter allows the input reference frequency

(REFIN) to be divided down to produce the reference clock

to the PFD. Division ratios from 1 to 1023 are allowed.

PHASE FREQUENCY DETECTOR (PFD) AND HIGH

VOLTAGE CHARGE PUMP

The phase frequency detector (PFD) takes inputs from the

R counter and N counter and produces an output proportional

to the phase and frequency difference between them. Figure 16

is a simplified schematic of the phase frequency detector.

HIGH

+IN

UP

D1 Q1

U1

CLR1

DELAY

U3

CHARGE

PUMP

CPOUT

HIGH

–IN

CLR2 DOWN

D2 Q2

U2

Figure 16. PFD Simplified Schematic

The PFD includes a delay element that sets the width of the

antibacklash pulse to 4.2 ns. This pulse ensures that there is

no dead zone in the PFD transfer function and provides a

consistent reference spur level.

The high voltage charge pump is designed on an Analog

Devices, Inc., proprietary high voltage process and allows the

charge pump to output voltages as high as 29 V when powered

by a 30 V supply. The high voltage charge pump removes the

need for active filtering when interfacing to a high voltage VCO.

Rev. 0 | Page 11 of 28

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet ADF4150HV.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADF4150HV | Fractional-N/Integer-N PLL Synthesizer | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |