|

|

PDF CY14C101PA Data sheet ( Hoja de datos )

| Número de pieza | CY14C101PA | |

| Descripción | 1-Mbit (128 K X 8) Serial (SPI) nvSRAM | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY14C101PA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PRELIMINARY

CY14C101PA

CY14B101PA

CY14E101PA

1-Mbit (128 K × 8) Serial (SPI) nvSRAM

with Real Time Clock

Features

■ 1-Mbit nonvolatile static random access memory (nvSRAM)

❐ Internally organized as 128 K × 8

❐ STORE to QuantumTrap nonvolatile elements initiated

automatically on power-down (AutoStore) or by using SPI

instruction (Software STORE) or HSB pin (Hardware

STORE)

❐ RECALL to SRAM initiated on power-up (Power Up RECALL)

or by SPI instruction (Software RECALL)

❐ Automatic STORE on power-down with a small capacitor

■ High reliability

❐ Infinite read, write, and RECALL cycles

❐ 1 million STORE cycles to QuantumTrap

❐ Data retention: 20 years at 85 °C

■ Real time clock (RTC)

❐ Full-featured RTC

❐ Watchdog timer

❐ Clock alarm with programmable interrupts

❐ Backup power fail indication

❐ Square wave output with programmable frequency

(1 Hz, 512 Hz, 4096 Hz, 32.768 kHz)

❐ Capacitor or battery backup for RTC

❐ Backup current of 0.45 uA (typical)

■ 40 MHz, and 104 MHz High-speed serial peripheral interface

(SPI)

❐ 40 MHz clock rate SPI write and read with zero cycle delay

❐ 104 MHz clock rate SPI write and read (with special fast read

instructions)

❐ Supports SPI mode 0 (0,0) and mode 3 (1,1)

■ SPI access to special functions

❐ Nonvolatile STORE/RECALL

❐ 8-byte serial number

❐ Manufacturer ID and Product ID

❐ Sleep mode

■ Write protection

❐ Hardware protection using Write Protect (WP) pin

❐ Software protection using Write Disable instruction

❐ Software block protection for 1/4, 1/2, or entire array

■ Low power consumption

❐ Average active current of 3 mA at 40 MHz operation

❐ Average standby mode current of 250 uA

❐ Sleep mode current of 8 uA

■ Industry standard configurations

❐ Operating voltages:

• CY14C101PA : VCC = 2.4 V to 2.6 V

• CY14B101PA : VCC = 2.7 V to 3.6 V

• CY14E101PA : VCC = 4.5 V to 5.5 V

❐ Industrial temperature

❐ 16-pin small outline integrated circuit (SOIC) package

❐ Restriction of hazardous substances (RoHS) compliant

Overview

The Cypress CY14X101PA combines a 1 Mbit nvSRAM[1] with a

full-featured RTC in a monolithic integrated circuit with serial SPI

interface. The memory is organized as 128 K words of 8 bits

each. The embedded nonvolatile elements incorporate the

QuantumTrap technology, creating the world’s most reliable

nonvolatile memory. The SRAM provides infinite read and write

cycles, while the QuantumTrap cells provide highly reliable

nonvolatile storage of data. Data transfers from SRAM to the

nonvolatile elements (STORE operation) takes place

automatically at power-down. On power-up, data is restored to

the SRAM from the nonvolatile memory (RECALL operation).

You can also initiate the STORE and RECALL operations

through SPI instruction.

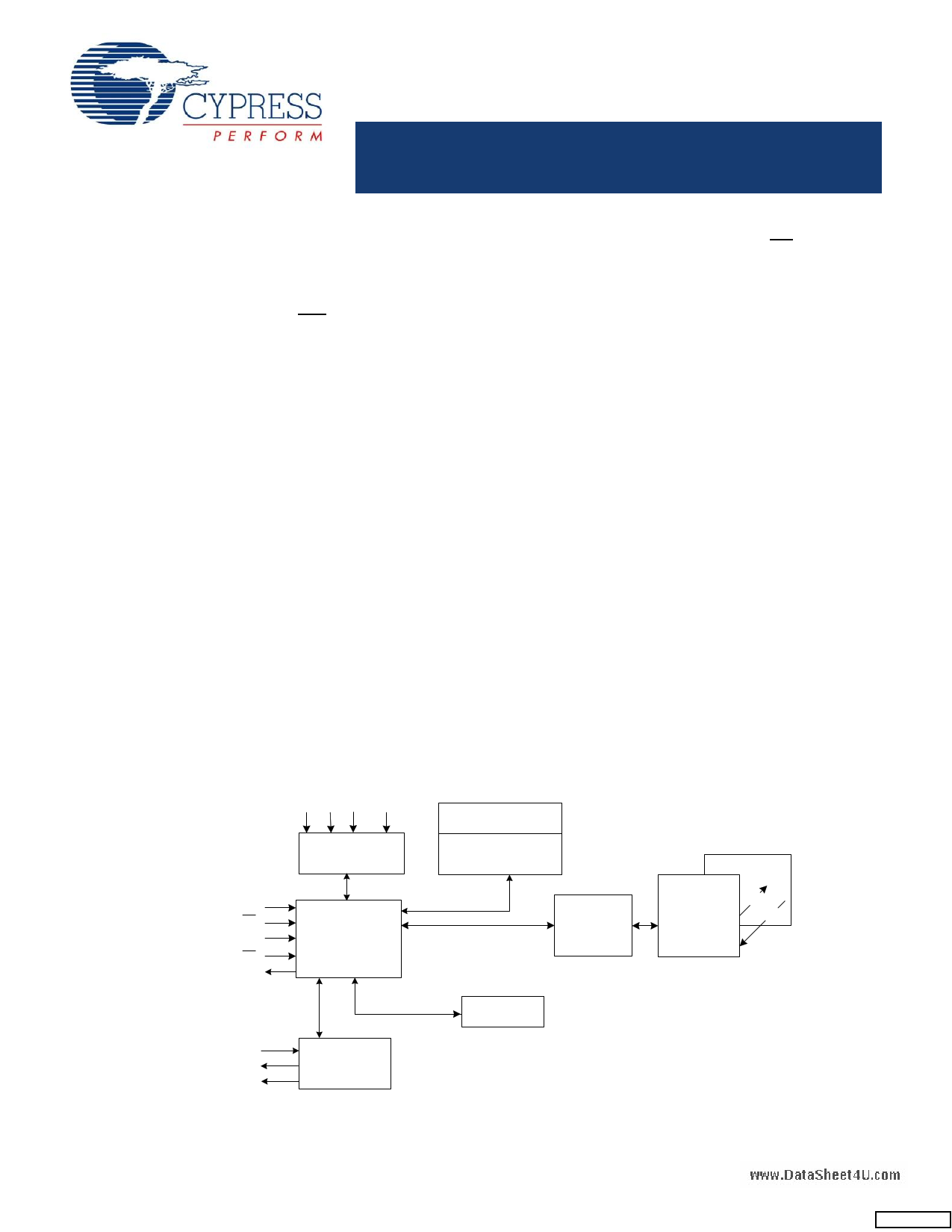

Logic Block Diagram

VCC VCAP VRTCcap VRTCbat

Serial Number

8x8

SI

CS

SCK

WP

SO

Power Control

Block

SLEEP

SPI Control Logic

Write Protection

Instruction decoder

Manufacture ID/

Product ID

RDSN/WRSN/RDID

READ/WRITE

STORE/RECALL/ASENB/ASDISB

Memory Data

&

Address Control

Quantrum Trap

128 K x 8

SRAM

128 K x 8

STORE

RECALL

www.DataSheet4U.com

RDRTC/WRTC

WRSR/RDSR/WREN

Status Register

Xin

INT/SQW

Xout

RTC Control Logic

Registers

Counters

Note

1. This device will be referred to as nvSRAM throughout the document.

Cypress Semiconductor Corporation • 198 Champion Court

Document #: 001-54392 Rev. *C

• San Jose, CA 95134-1709 • 408-943-2600

Revised January 21, 2011

[+] Feedback

1 page

PRELIMINARY

CY14C101PA

CY14B101PA

CY14E101PA

to complete the Store. This corrupts the data stored in the

nvSRAM and Status Register. To resume normal functionality,

the WRSR instruction must be issued to update the nonvolatile

bits BP0, BP1, and WPEN in the Status Register.

Figure 2 shows the proper connection of the storage capacitor

(VCAP) for AutoStore operation. Refer to DC Electrical Charac-

teristics on page 32 for the size of the VCAP.

Figure 2. AutoStore Mode

VCC

0.1uF

VCC

CS VCAP

VSS

VCAP

Software STORE Operation

Software STORE allows the user to trigger a STORE operation

through a special SPI instruction. STORE operation is initiated

by executing STORE instruction regardless of whether or not a

write has been performed since the last NV operation.

A STORE cycle takes tSTORE time to complete, during which all

the memory accesses to nvSRAM are inhibited. The RDY bit of

the Status Register or the HSB pin may be polled to find the

Ready/Busy status of the nvSRAM. After the tSTORE cycle time

is completed, the SRAM is activated again for read and write

operations.

Hardware STORE and HSB pin Operation

The HSB pin in CY14X101PA is used to control and

acknowledge STORE operations. If no STORE/RECALL is in

progress, this pin can be used to request a Hardware STORE

cycle. When the HSB pin is driven LOW, the CY14X101PA

conditionally initiates a STORE operation after tDELAY duration.

A STORE cycle starts only if a write to the SRAM has been

performed since the last STORE or RECALL cycle. Reads and

Writes to the memory are inhibited for tSTORE duration or as long

as HSB pin is LOW. The HSB pin also acts as an open drain

driver (internal 100 kΩ weak pull up resistor) that is internally

driven LOW to indicate a busy condition when the STORE

www(.iDniatitaatSehdebety4aUn.cyommeans) is in progress.

Note After each Hardware and Software STORE operation, HSB

is driven HIGH for a short time (tHHHD) with standard output high

current and then remains HIGH by an internal 100 kΩ pull-up

resistor.

Note For successful last data byte STORE, a hardware STORE

should be initiated at least one clock cycle after the last data bit

D0 is received.

Upon completion of the STORE operation, the nvSRAM memory

access is inhibited for tLZHSB time after HSB pin returns HIGH.

The HSB pin must be left unconnected if not used.

RECALL Operation

A RECALL operation transfers the data stored in the nonvolatile

QuantumTrap elements to the SRAM. In CY14X101PA, a

RECALL may be initiated in two ways: Hardware RECALL,

initiated on power-up and Software RECALL, initiated by a SPI

RECALL instruction.

Internally, RECALL is a two step procedure. First, the SRAM data

is cleared. Next, the nonvolatile information is transferred into the

SRAM cells. All memory accesses are inhibited while a RECALL

cycle is in progress. The RECALL operation does not alter the

data in the nonvolatile elements.

Hardware RECALL (Power Up)

During power-up, when VCC crosses VSWITCH, an automatic

RECALL sequence is initiated, which transfers the content of

nonvolatile memory on to the SRAM.

A Power Up RECALL cycle takes tFA time to complete and the

memory access is disabled during this time. HSB pin is used to

detect the Ready status of the device.

Software RECALL

Software RECALL allows you to initiate a RECALL operation to

restore the content of nonvolatile memory on to the SRAM. In

CY14X101PA, this can be done by issuing a RECALL instruction

in SPI.

A Software RECALL takes tRECALL time to complete during

which all memory accesses to nvSRAM are inhibited. The

controller must provide sufficient delay for the RECALL operation

to complete before issuing any memory access instructions.

Disabling and Enabling AutoStore

If the application does not require the AutoStore feature, it can

be disabled in CY14X101PA by using the ASDISB instruction. If

this is done, the nvSRAM does not perform a STORE operation

at power-down.

AutoStore can be re enabled by using the ASENB instruction.

However, these operations are not nonvolatile and if you need

this setting to survive the power cycle, a STORE operation must

be performed following AutoStore Disable or Enable operation.

Note CY14X101PA comes from the factory with AutoStore

Enabled.

Note If AutoStore is disabled and VCAP is not required, then the

VCAP pin must be left open. The VCAP pin must never be

connected to ground. The Power Up RECALL operation cannot

be disabled in any case.

Document #: 001-54392 Rev. *C

Page 5 of 44

[+] Feedback

5 Page

PRELIMINARY

CY14C101PA

CY14B101PA

CY14E101PA

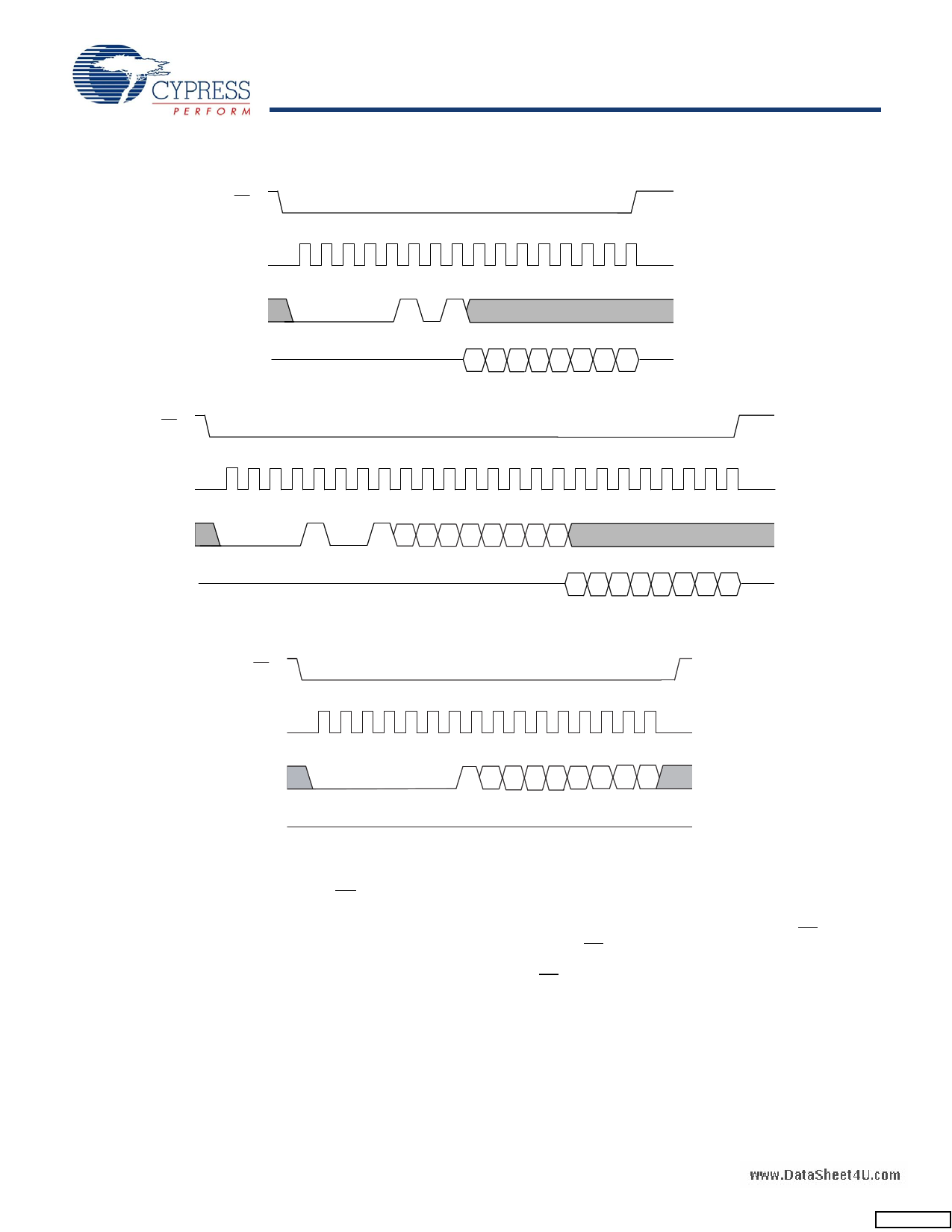

Figure 6. Read Status Register (RDSR) Instruction Timing

CS

SCK

SI

0 1 2 3 4 5 67 01 2 3 4 5 67

Op-Code

0 0 0 0 01 0 1 0

CS

SCK

SI

SO HI-Z D7 D6 D5 D4 D3 D2 D1 D0

MSB

Data

LSB

Figure 7. Fast Read Status Register (FAST_RDSR) Instruction Timing

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7

Op-Code

Dummy Byte

0 0 0 0 1 00 1 XXXXX XXX 0

SO

HI-Z

D7 D6 D5 D4 D3 D2 D1 D0

MSB

Data

LSB

Figure 8. Write Status Register (WRSR) Instruction Timing

CS

SCK

01 23 4 5 6 701 2 3 4 5 6 7

Opcode

Data in

SI 0 0 0 0 0 0 0 1 D7 X X X D3 D2 X X

MSB

LSB

SO HI-Z

Write Protection and Block Protection

CY14X101PA provides features for both software and hardware

write protection using WRDI instruction and WP. Additionally, this

device also provides block protection mechanism through BP0

and BP1 pins of the Status Register.

The write enable and disable status of the device is indicated by

WEN bit of the Status Register. The write instructions (WRSR,

WRITE, and WRTC) and nvSRAM special instruction (STORE,

wwwR.EDCaAtaLSLh,eAeSt4EUN.cBo,mASDISB) need the write to be enabled (WEN

bit = ‘1’) before they can be issued.

Write Enable (WREN) Instruction

On power-up, the device is always in the write disable state. The

following WRITE, WRSR, WRTC, or nvSRAM special instruction

must therefore be preceded by a Write Enable instruction. If the

device is not write enabled (WEN = ‘0’), it ignores the write

instructions and returns to the standby state when CS is brought

HIGH. A new CS falling edge is required to re-initiate serial

communication. The instruction is issued following the falling

edge of CS. When this instruction is used, the WEN bit of Status

Register is set to ‘1’. WEN bit defaults to ‘0’ on power-up.

Note After completion of a write instruction (WRSR, WRITE, or

WRTC) or nvSRAM special instruction (STORE, RECALL,

ASENB, ASDISB) instruction, WEN bit is cleared to ‘0’. This is

done to provide protection from any inadvertent writes.

Therefore, WREN instruction needs to be used before a new

write instruction can be issued

Document #: 001-54392 Rev. *C

Page 11 of 44

[+] Feedback

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CY14C101PA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY14C101PA | 1-Mbit (128 K X 8) Serial (SPI) nvSRAM | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |