|

|

PDF LP2995LQ Data sheet ( Hoja de datos )

| Número de pieza | LP2995LQ | |

| Descripción | DDR Termination Regulator | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LP2995LQ (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

July 2003

LP2995

DDR Termination Regulator

General Description

The LP2995 linear regulator is designed to meet the JEDEC

SSTL-2 and SSTL-3 specifications for termination of DDR-

SDRAM. The device contains a high-speed operational am-

plifier to provide excellent response to load transients. The

output stage prevents shoot through while delivering 1.5A

continuous current and transient peaks up to 3A in the

application as required for DDR-SDRAM termination. The

LP2995 also incorporates a VSENSE pin to provide superior

load regulation and a VREF output as a reference for the

chipset and DDR DIMMS.

Patents Pending

Features

n Low output voltage offset

n Works with +5v, +3.3v and 2.5v rails

n Source and sink current

n Low external component count

n No external resistors required

n Linear topology

n Available in SO-8, PSOP-8 or LLP-16 packages

n Low cost and easy to use

Applications

n DDR Termination Voltage

n SSTL-2

n SSTL-3

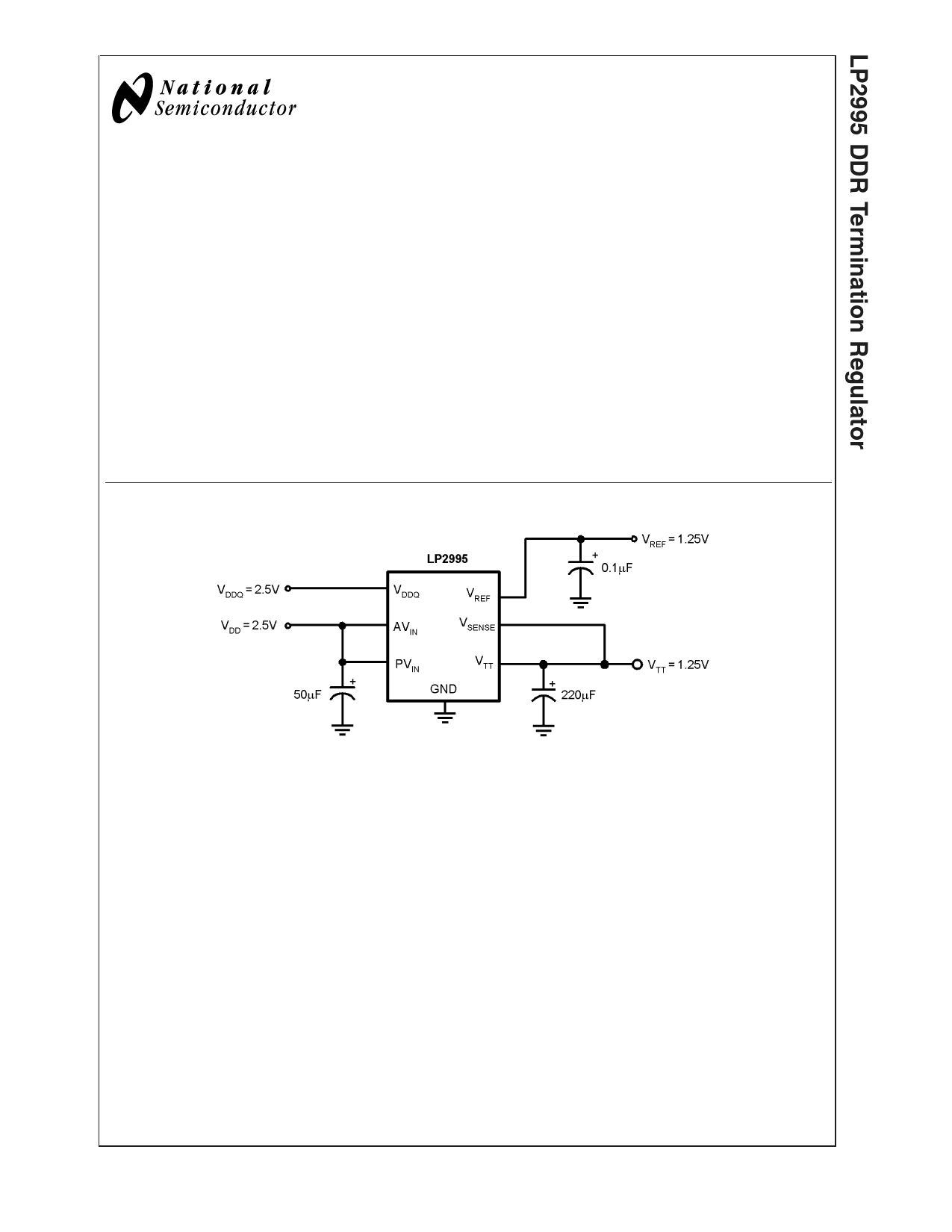

Typical Application Circuit

20039302

© 2003 National Semiconductor Corporation DS200393

www.national.com

1 page

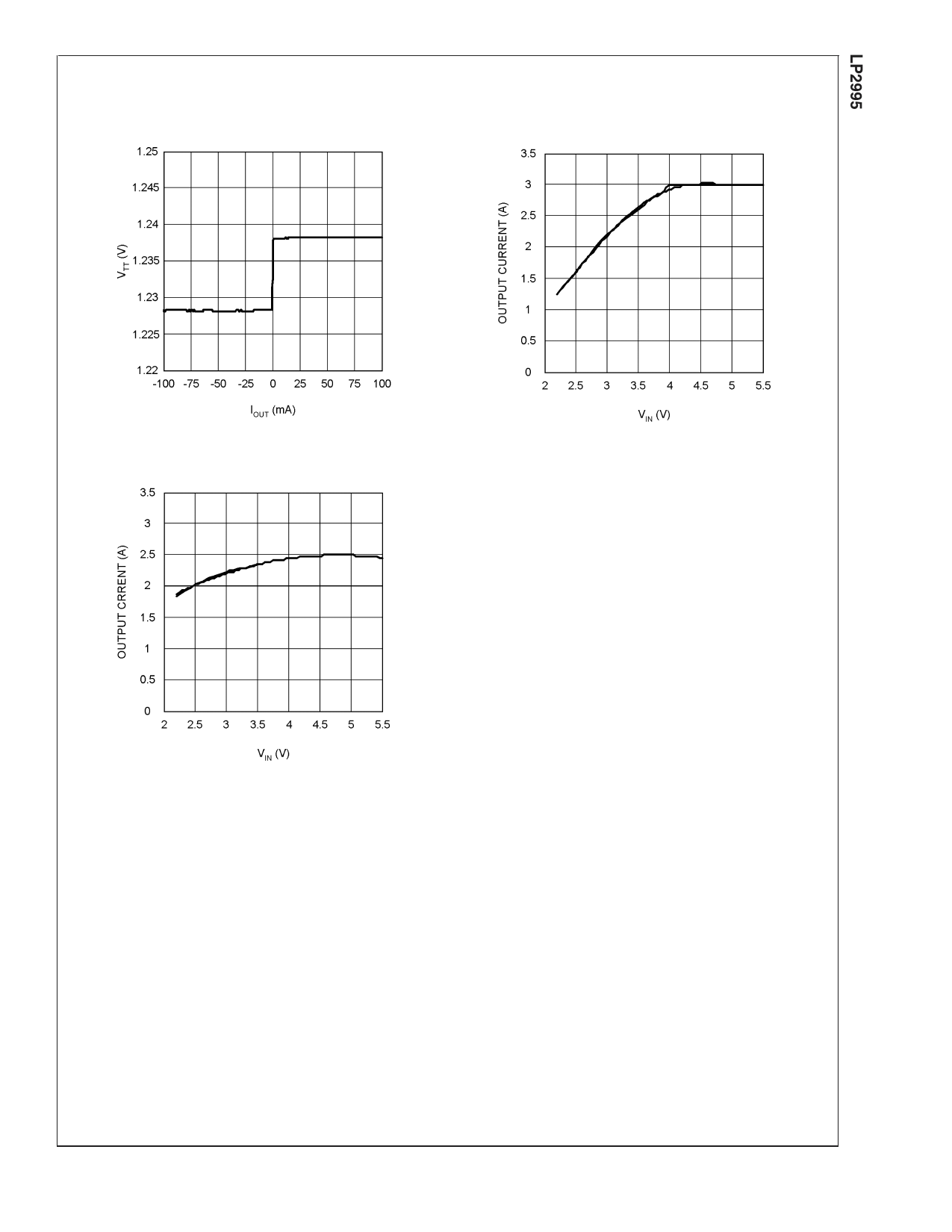

Typical Performance Characteristics (Continued)

VTT vs IOUT

Maximum Output Current (Sourcing) vs VIN

(VDDQ = 2.5)

20039315

Maximum Output Current (Sinking) vs VIN

(VDDQ = 2.5)

20039316

20039317

5 www.national.com

5 Page

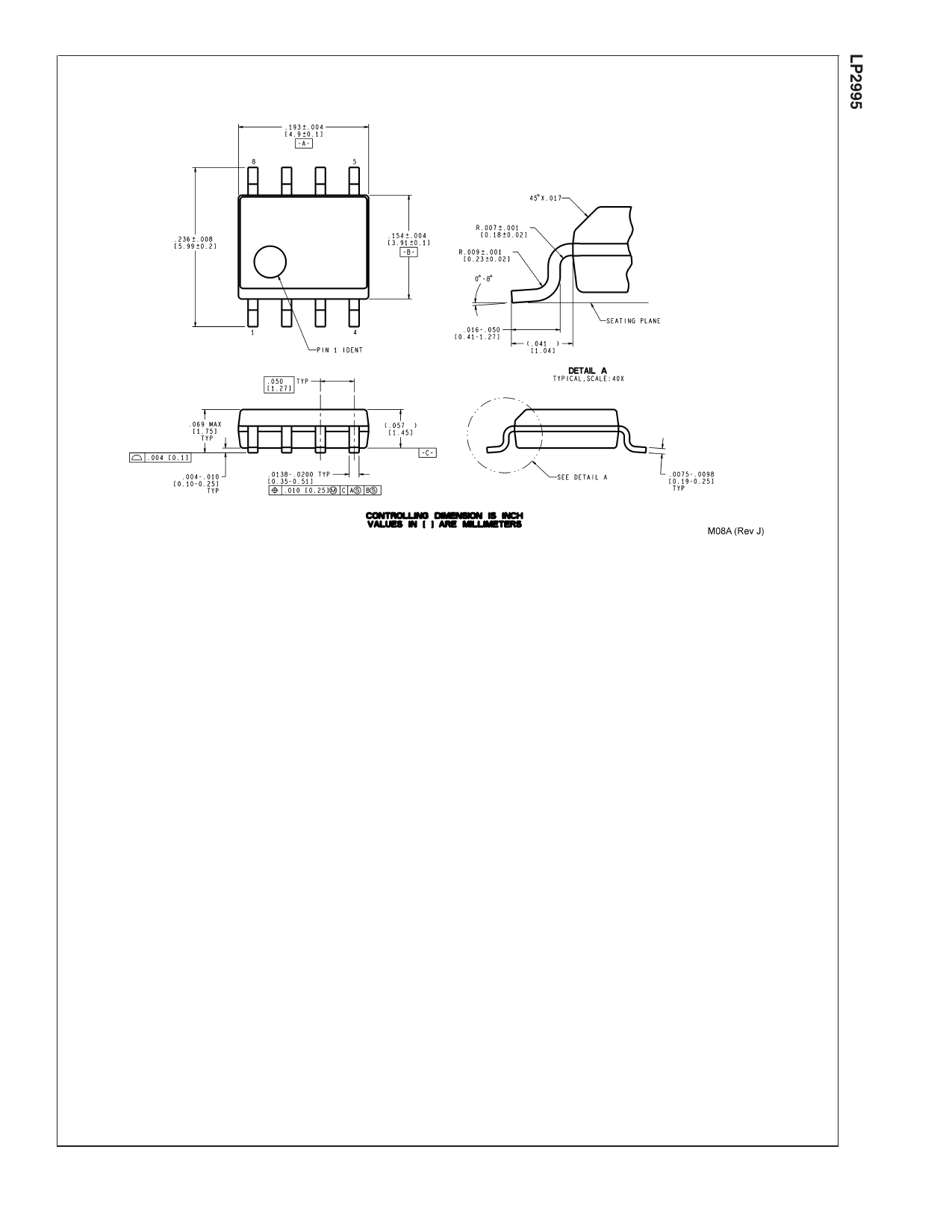

Physical Dimensions inches (millimeters)

unless otherwise noted

8-Lead Small Outline Package (M8)

NS Package Number M08A

11 www.national.com

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet LP2995LQ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LP2995LQ | DDR Termination Regulator | National Semiconductor |

| LP2995LQ | DDR Termination Regulator | National Semiconductor |

| LP2995LQX | DDR Termination Regulator | National Semiconductor |

| LP2995LQX | DDR Termination Regulator | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |