|

|

PDF CE2766 Data sheet ( Hoja de datos )

| Número de pieza | CE2766 | |

| Descripción | 6-Channe Audio DAC | |

| Fabricantes | CEI | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CE2766 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

Microelectronics

CE2766

6-Channel Audio DAC, 24-bit, 192kHz

DESCRIPTION

The CE2766 is a mixed signal CMOS monolithic audio

digital to analog converter. It contains six multi-bit sigma

delta DAC. The system consists of 128-time interpolation

filters, 4th order Σ∆ modulators, switch capacitors and

www.DataSheet4Uoanf.cfaeolrmosgsurpeceorinosrtrduicffteiorenntfiialtlelrisn.eaTrhitey,

one bit

with no

Σ∆ converter

distortion due

to component mis-match. high tolerance to clock jitter.

The CE2766 support data conversion from 32K to

192KHz. The chip is operated at 3.3 volt to simplify the

power requirement. The CE2766 is ideal for DVD player,

AV receiver and set-top box application.

The CE2766 support 32, 24, 20 and 16-bit input data. It

also support multiple sampling frequency data. Each DAC

has its own individual volume control.

FEATURES

• Six Channel Audio DAC.

- 101 dB SNR (A Weighted).

- -86 dB THD + N Ratio (A Weighted).

- 32K - 192 KHz. Sampling Rates.

- Independent Digital Volume Control.

- I2S, Left and Right Justified Digital Input Formats.

- On -chip Reconstruction Filters.

• 2-wire Serial Control Interface.

• Single 3.3 Volt Power Supply.

Applications

• Digital Surround Sound For Home Theatre

• DVD

• Car Audio.

XCK PLL

DIN1

DIN2

DIN3

80

80

77

LRCK

BCK

77

78

DIGITAL

AUDIO

INPUT

Clock Rate

Detect'n

CEI Microelectronics Co. Ltd.

CE2766

INTERPOLATION

FILTER

Σ∆

Mod.

Σ∆

Mod.

Σ∆

Mod.

D/A

D/A

D/A

D/A

D/A

D/A

Control Interface

SDA

SCL

15

RST

15

VCM

AR1

AL1

AR2

AL2

AR3

AL3

1-19 June 25, 2005

1 page

CE2766

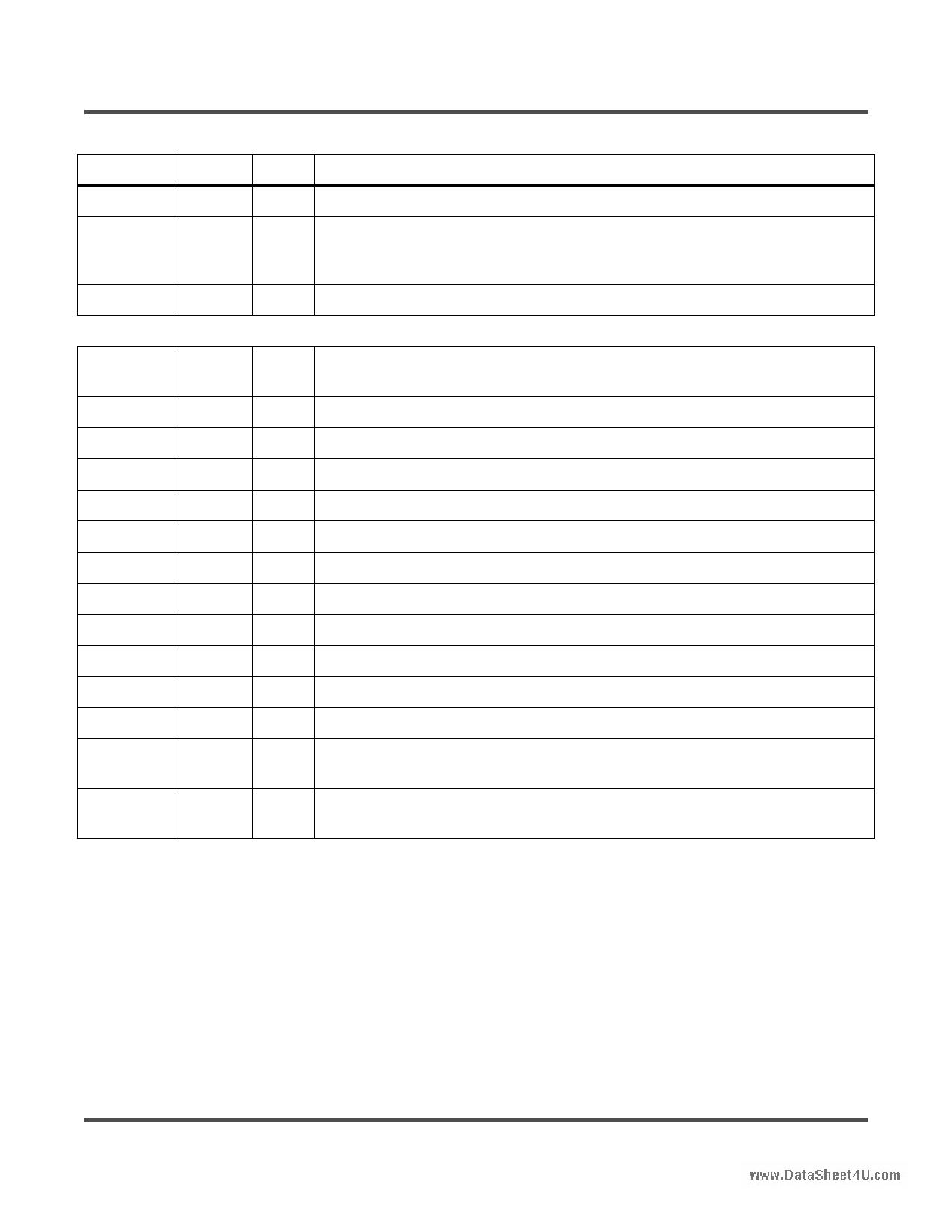

PIN DESCRIPTION (Continued)

Pin Name

TSTOUT

SDA

Pin #

12

13

Type

T

I/O

Description

Tri-state output pin, This pin can be connected to ground or leave open

I2C data bus. Open drain output. Externally this pin should tie to a 680 ohm pull up

resistor.

SCL

Analog

www.DataSheeAt4VUD.coDm

AR1

GR0

AL1

AGND

AR2

GR1

AL2

AGND

AR3

GR2

AL3

VCM

AVDD

14 I I2C clock input.

28 +3.3V Analog circuits power supply.Should be Connected to a 100 uF capacitor in parallel

with a 1 uF.

27 O Analog right channel 1 output

26 GND Analog circuits ground

25 O Analog left channel 1 output

24 GND Analog circuits ground

23 O Analog right channel 2 output

22 GND Analog circuits ground

21 O Analog left channel 2 output

20 GND Analog circuits ground

19 O Analog right channel 3 output

18 GND Analog circuits ground

17 O Analog right channel 3 output

16 I/O Common voltage De-coupling Pin Should be Connected to a 20 uF capacitor in parallel

with a 1 uF.

15 +3.3V Analog circuits power supply.Should be Connected to a a 100 uF. in parallel with a 1

uF.

5-19 June 25, 2005

5 Page

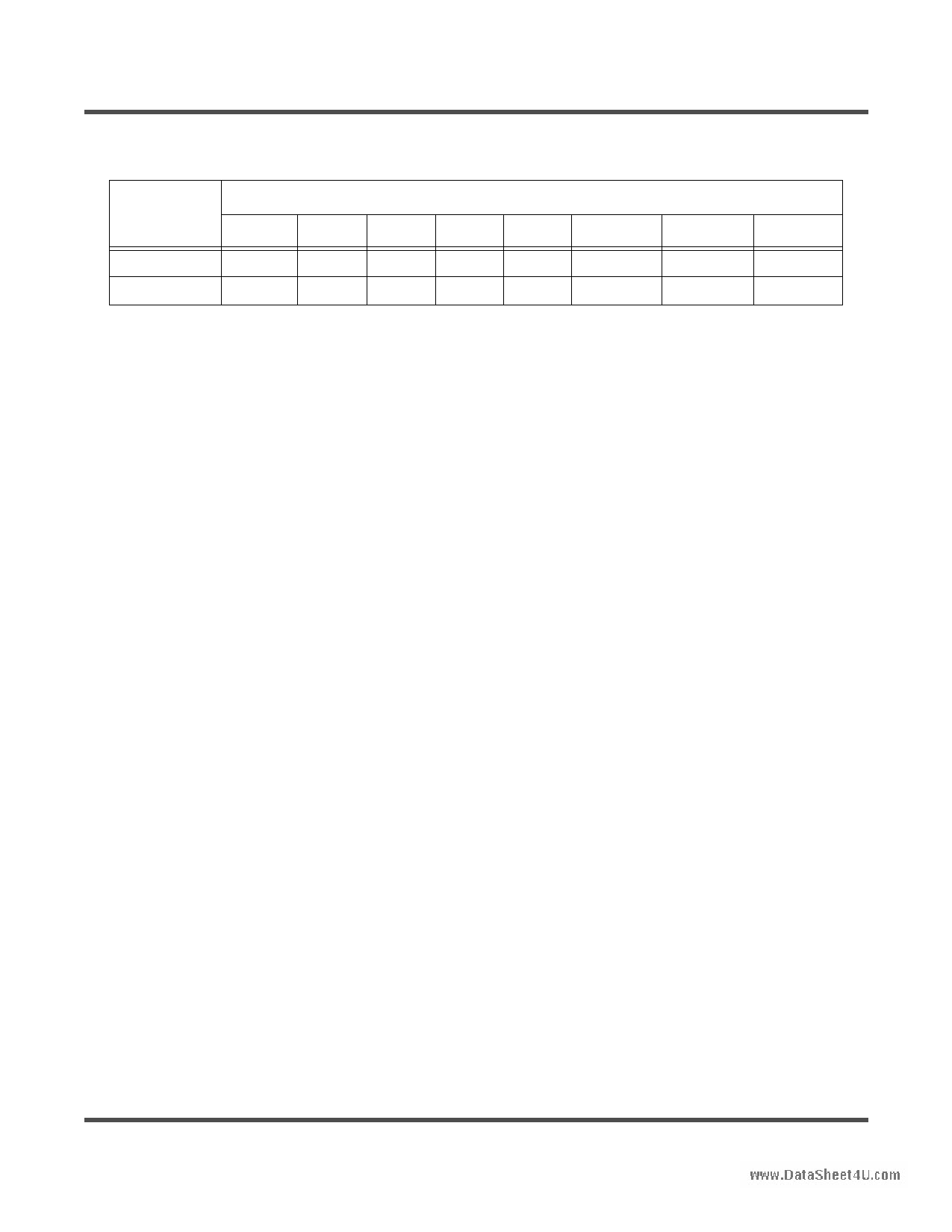

CE2766

Control Register 1 (ADRS=hex01, default=hex80)

ADDR[3:0]

Hex 01

Default Value

BIT 7

AUTODET

1

BIT 6

FS384

0

CREG1[7:0]

BIT 5

CKDIV4

0

BIT 4

CKDIV2

0

BIT 3

CKdet

0

BIT 2

MUTE56

0

BIT 1

MUTE34

0

BIT 0

MUTE12

0

AUTODET Automatically detects the serial audio input data sampling rate clock frequency.

www.DataSheet4U.com

0: - do not use auto-detect

1: - automatically detects the serial audio input data sampling rate and clock frequency.

FS384: 384 fs or 256 fs control for the PLL clock output. This bit is recognized only when “AUTODET” bit is set to ‘0’

otherwise the input format is automatically detected.

0: the PLL takes the reference clock and multiplies it by 2 to generate a 512 bit clock

1: the PLL takes the reference clock and multiplies it by 4/3 to generate a 512 bit clock

CKDIV4: Clock divider enable control.This bit is recognized only when “AUTODET” bit is set to ‘0’ otherwise the input

format is automatically detected.

0: do not enable input clock divided by 4

1: enable input clock divided by 4

CKDIV2: Clock divider enable control . This bit is recognized only when “AUTODET” bit is set to ‘0’ otherwise the

input format is automatically detected.

0: do not enable input clock divided by 2

1: enable input clock divided by 2

CKdet: turn off clock detection.

0: enable clock detection. The chip will be in reset mode when there are no clock.

1: disable clock detection.

MUTE56: Mute control for channels 5 and 6

0: do not mute channels 5 and 6

1: simultaneously mute channels 5 and 6

MUTE34: Mute control for channels 3 and 4

0: do not mute channels 3 and 4

1: simultaneously mute channels 3 and 4

MUTE12: Mute control for channels 1 and 2

0: do not mute channels 1 and 2

1: simultaneously mute channels1 and2

11-19

June 25, 2005

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CE2766.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CE2766 | 6-Channe Audio DAC | CEI |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |