|

|

PDF AZ10LVEL33 Data sheet ( Hoja de datos )

| Número de pieza | AZ10LVEL33 | |

| Descripción | ECL/PECL / 4 Divider | |

| Fabricantes | Arizona Microtek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AZ10LVEL33 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

AZ10LVEL33

AZ100LVEL33

ARIZONA MICROTEK, INC.

ECL/PECL ÷4 Divider

FEATURES

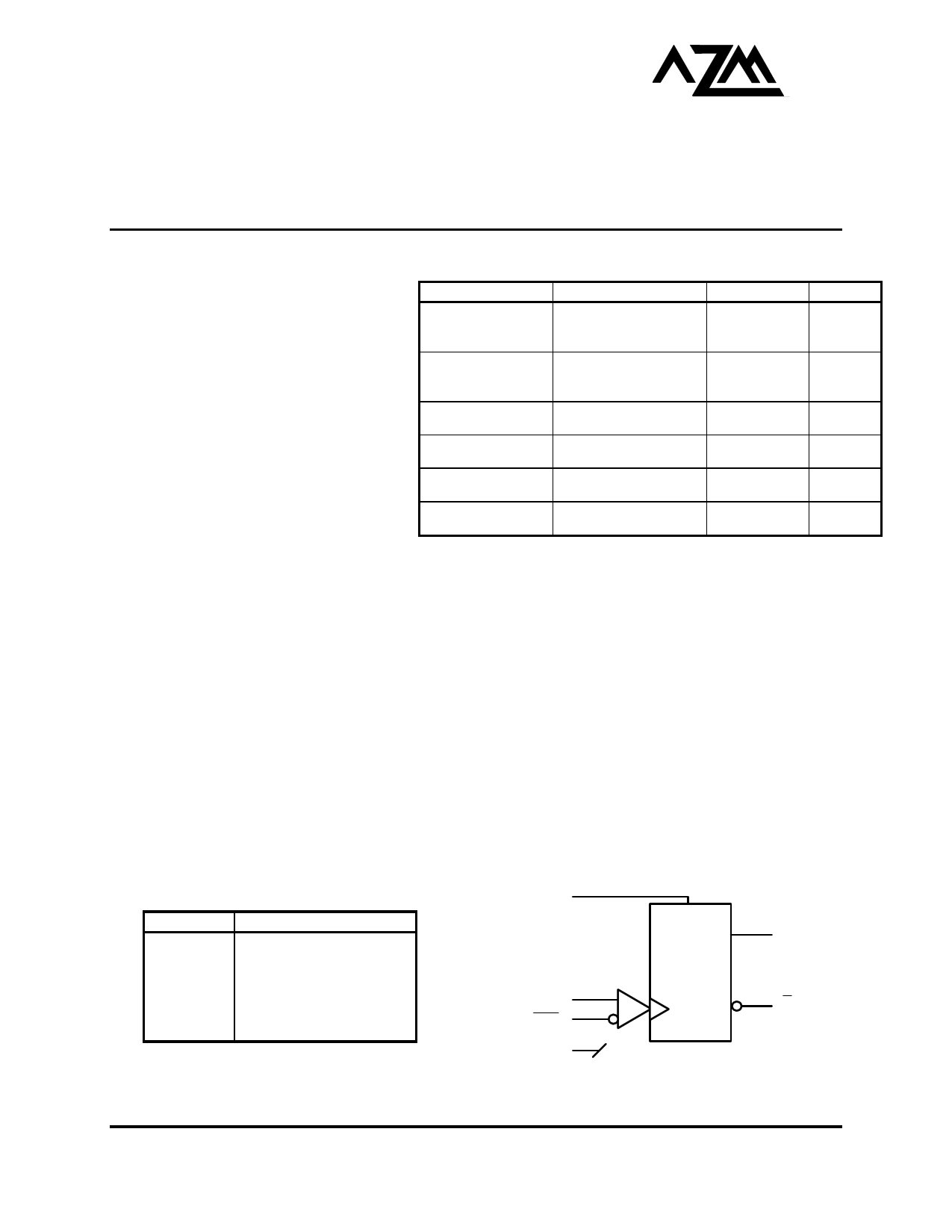

PACKAGE AVAILABILITY

• Green / RoHS Compliant /

Lead (Pb) Free package available

• Operating Range of 3.0V to 5.5V

PACKAGE

MLP 8 (2x2) Green

/ RoHS Compliant /

Lead (Pb) Free

PART NUMBER

AZ100LVEL33NG

MARKING

C3G

<Date Code>

NOTES

1,2

• 470ps Propagation Delay

• 4.0GHz Toggle Frequency

MLP 16 (3x3)

• Internal Input Pulldown Resistors

• Direct Replacement for ON Semiconductor SOIC 8

MC10EL33, MC100EL33,

and MC100LVEL33

SOIC 8

• Transistor Count = 91 Devices

• IBIS Model Files Available on Arizona

TSSOP 8

AZ10/100LVEL33L

AZ10LVEL33D

AZ100LVEL33D

AZ10LVEL33T

AZM

L33

<Date Code>

AZM10

LVEL33

AZM100

LVEL33

AZT

LV33

1,2

1,2,3

1,2,3

1,2,3

Microtek Web Site

TSSOP 8

AZ100LVEL33T

AZH

LV33

1,2,3

1 Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K

parts) Tape & Reel.

2 Date code format: “Y” or “YY” for year followed by “WW” for week.

3 Date code “YWW” or “YYWW” on underside of part.

DESCRIPTION

The AZ10/100LVEL33 is an integrated ÷4 divider. The RESET pin is asynchronous and clears the output (Q

Low, Q¯ High) on the rising edge. Upon power-up, the internal flip-flop will be in a random logic state. RESET

allows for the synchronization of multiple LVEL33’s in a system.

The LVEL33 provides a VBB output for single-end use or a DC bias reference for AC coupling to the device.

For single-ended input applications, the VBB reference should be connected to one side of the CLK/ C¯¯L¯K¯ differential

input pair. The input signal is then fed to the other CLK/ C¯¯L¯K¯ input. The VBB pin can support 1.0mA sink/source

current. When used, the VBB pin should be bypassed to ground via a 0.01μF capacitor.

NOTE: Specifications in the ECL/PECL tables are valid when thermal equilibrium is established.

PIN DESCRIPTION

PIN

CLK, C¯L¯¯K

RESET

VBB

Q, Q¯

VCC

VEE

FUNCTION

Clock Inputs

Asynchronous Reset

Reference Voltage Output

Data Outputs

Positive Supply

Negative Supply

RESET

CLK

CLK

VBB

LOGIC DIAGRAM

R

Q

÷4

Q

1630 S. STAPLEY DR., SUITE 127 • MESA, ARIZONA 85204 • USA • (480) 962-5881 • FAX (480) 890-2541

www.azmicrotek.com

1 page

AZ10LVEL33

AZ100LVEL33

AZ10/100LVEL33L

RESET NC NC VCC

16 15 14 13

PACKAGE PINOUTS

TOP VIEW

AZ100LVEL33N

NC 1

12 NC

RESET 1

CLK 2

CLK 3

MLP16

11 Q

10 Q

VBB 4

56

NC NC

9 NC

78

VEE 10K

CLK 2

CLK 3

VBB 4

MLP 8

8 VCC

7Q

6Q

5 VEE

100K Mode: Leave the 10K pin open (NC)

10K Mode: Connect the 10K pin to VEE

Bottom Center Pad may be left open or tied to VEE.

Bottom Center Pad may be left open or tied to VEE.

AZ10LVEL33D

AZ100LVEL33D

AZ10LVEL33T

AZ100LVEL33T

RESET 1

8 VCC

CLK 2

CLK 3

SOIC 8

TSSOP 8

7Q

6Q

VBB 4

5 VEE

April 2007 * REV - 9

www.azmicrotek.com

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet AZ10LVEL33.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AZ10LVEL32 | ECL/PECL / 2 Divider | Arizona Microtek |

| AZ10LVEL33 | ECL/PECL / 4 Divider | Arizona Microtek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |