|

|

PDF NB100LVEP56 Data sheet ( Hoja de datos )

| Número de pieza | NB100LVEP56 | |

| Descripción | ECL Dual Differential 2:1 Multiplexer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB100LVEP56 (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

NB100LVEP56

2.5V / 3.3V ECL DUAL

Differential 2:1 Multiplexer

Description

The NB100LVEP56 is a dual, fully differential 2:1 multiplexer. The

differential data path makes the device ideal for multiplexing low

skew clock or differential data signals. The device features both

individual and common select inputs to address both data path and

random logic applications. Common and individual selects can accept

both LVECL and LVCMOS input voltage levels. Multiple VBB pins

are provided.

The VBB pin, an internally generated voltage supply, is available to

this device only. For single−ended input operation, the unused

differential input is connected to VBB as a switching reference voltage.

VBB may also rebias AC coupled inputs. When used, decouple VBB

and VCC via a 0.01 mF capacitor and limit current sourcing or sinking

to 0.5 mA. When not used, VBB should be left open.

Features

• Maximum Input Clock Frequency > 2.5 GHz Typical

• Maximum Input Data Rate > 2.5 Gb/s Typical

• 525 ps Typical Propagation Delays

• Low Profile QFN Package

• PECL Mode Operating Range:

VCC = 2.375 V to 3.8 V with VEE = 0 V

• NECL Mode Operating Range:

VCC = 0 V with VEE = −2.375 V to −3.8 V

• Separate, Common Select, and Individual Select

(Compatible with ECL and CMOS Input Voltage Levels)

• Q Output Will Default LOW with Inputs Open or at VEE

• Multiple VBB Outputs

• These Devices are Pb−Free and are RoHS Compliant

www.onsemi.com

MARKING

DIAGRAMS*

TSSOP−20 WB

DT SUFFIX

CASE 948E

N100

VP56

ALYWG

G

24 1

QFN24

MN SUFFIX

CASE 485L

24

1

N100

VP56

ALYWG

G

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

*For additional marking information, refer to

Application Note AND8002/D.

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 8 of this data sheet.

© Semiconductor Components Industries, LLC, 2016

February, 2016 − Rev. 11

1

Publication Order Number:

NB100LVEP56/D

1 page

NB100LVEP56

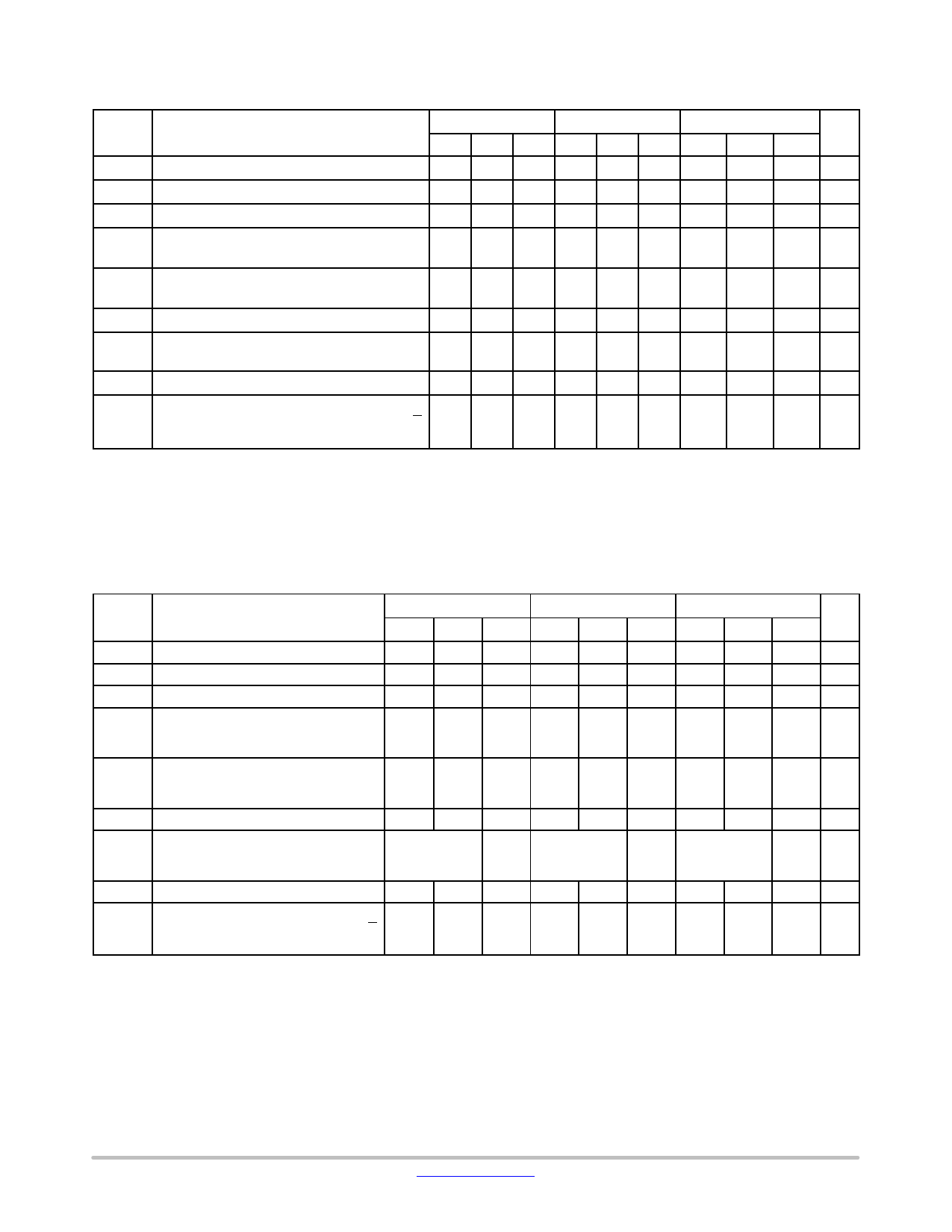

Table 6. DC CHARACTERISTICS, PECL VCC = 3.3 V, VEE = 0 V (Note 6)

−40°C

Symbol

Characteristic

Min Typ Max

IEE Negative Power Supply Current

35 45 55

VOH Output HIGH Voltage (Note 7)

2155 2280 2405

VOL Output LOW Voltage (Note 7)

1355 1575 1700

VIH Input HIGH Voltage (SEL0, SEL1, COM_SEL) 2135

Input HIGH Voltage (D Inputs)

2135

VCC

2420

Min

35

2155

1355

2135

2135

25°C

Typ

45

2280

1575

Max

55

2405

1700

VCC

2420

Min

35

2155

1355

2135

2135

85°C

Typ

48

2280

1575

Max

58

2405

1700

VCC

2420

Unit

mA

mV

mV

mV

VIL Input LOW Voltage (SEL0, SEL1, COM_SEL) VEE

Input LOW Voltage (D Inputs)

1355

1675 VEE

1675 1355

1675 VEE

1675 1355

1675 mV

1675

VBB

VIHCMR

Output Reference Voltage (Note 8)

Input HIGH Voltage Common Mode Range

(Differential Configuration) (Note 9)

1775 1875 1975 1775 1875 1975 1775 1875 1975 mV

1.2 3.3 1.2 3.3 1.2

3.3 V

IIH Input HIGH Current (@VIH)

150 150

150 mA

IIL Input LOW Current (@VIL)

D 0.5

D −150

SEL −150

0.5

−150

−150

0.5

−150

−150

mA

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

6. Input and output parameters vary 1:1 with VCC. VEE can vary +0.5 V to −0.3 V.

7. All loading with 50 W to VCC − 2.0 V.

8. Single−Ended input operation is limited to VCC w 3.0 V in PECL mode.

9. VIHCMR min varies 1:1 with VEE, VIHCMR max varies 1:1 with VCC. The VIHCMR range is referenced to the most positive side of the differential

input signal.

Table 7. DC CHARACTERISTICS, NECL VCC = 0 V, VEE = −3.8 V to −2.375 V (Note 10)

−40°C

25°C

85°C

Symbol

IEE

VOH

VOL

VIH

Characteristic

Negative Power Supply Current

Output HIGH Voltage (Note 11)

Output LOW Voltage (Note 11)

Input HIGH Voltage

(SEL0, SEL1, COM_SEL)

Input HIGH Voltage (D Inputs)

Min Typ Max Min Typ Max Min Typ Max Unit

35 45 55 35 45 55 35 48 58 mA

−1145 −1020 −895 −1145 −1020 −895 −1145 −1020 −895 mV

−1945 −1725 −1600 −1945 −1725 −1600 −1945 −1725 −1600 mV

−1165

−1165

VCC −1165

−880 −1165

VCC −1165

−880 −1165

VCC

−880

mV

VIL Input LOW Voltage

(SEL0, SEL1, COM_SEL)

Input LOW Voltage (D Inputs)

VEE

−1945

−1600 VEE

−1600 −1945

−1600 VEE

−1600 −1945

mV

−1600

−1600

VBB

VIHCMR

Output Reference Voltage (Note 12)

Input HIGH Voltage Common Mode

Range (Differential Configuration)

(Note 13)

−1525 −1425 −1325 −1525 −1425 −1325 −1525 −1425 −1325 mV

VEE+1.2 0.0 VEE+1.2 0.0 VEE+1.2 0.0 V

IIH Input HIGH Current (@VIH)

IIL Input LOW Current (@VIL)

D 0.5

D −150

SEL −150

150

0.5

−150

−150

150

0.5

−150

−150

150 mA

mA

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

10. Input and output parameters vary 1:1 with VCC.

11. All loading with 50 W to VCC − 2.0 V.

12. Single−Ended input operation is limited to VEE from −3.0 V to −5.5 V in NECL mode.

13. VIHCMR min varies 1:1 with VEE, VIHCMR max varies 1:1 with VCC. The VIHCMR range is referenced to the most positive side of the differential

input signal.

www.onsemi.com

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet NB100LVEP56.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB100LVEP56 | ECL Dual Differential 2:1 Multiplexer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |