|

|

PDF 54AC74 Data sheet ( Hoja de datos )

| Número de pieza | 54AC74 | |

| Descripción | Dual D-Type Positive Edge-Triggered Flip-Flop | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 54AC74 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

August 1998

54AC74 • 54ACT74

Dual D-Type Positive Edge-Triggered Flip-Flop

General Description

The ’AC/’ACT74 is a dual D-type flip-flop with Asynchronous

Clear and Set inputs and complementary (Q, Q) outputs. In-

formation at the input is transferred to the outputs on the

positive edge of the clock pulse. Clock triggering occurs at a

voltage level of the clock pulse and is not directly related to

the transition time of the positive-going pulse. After the Clock

Pulse input threshold voltage has been passed, the Data in-

put is locked out and information present will not be trans-

ferred to the outputs until the next rising edge of the Clock

Pulse input.

Asynchronous Inputs:

LOW input to SD (Set) sets Q to HIGH level

LOW input to CD (Clear) sets Q to LOW level

Clear and Set are independent of clock

Simultaneous LOW on CD and SD makes both Q and Q

HIGH

Features

n ICC reduced by 50%

n Output source/sink 24 mA

n ’ACT74 has TTL-compatible inputs

n Standard Microcircuit Drawing (SMD)

— ’AC74: 5962-88520

— ’ACT74: 5962-87525

Logic Symbols

DS100266-1

IEEE/IEC

Pin Names

D1, D2

CP1, CP2

CD1, CD2

SD1, SD2

Q1, Q1, Q2, Q2

DS100266-2

Description

Data Inputs

Clock Pulse Inputs

Direct Clear Inputs

Direct Set Inputs

Outputs

DS100266-3

FACT® is a registered trademark of Fairchild Semiconductor Corporation.

© 1998 National Semiconductor Corporation DS100266

www.national.com

1 page

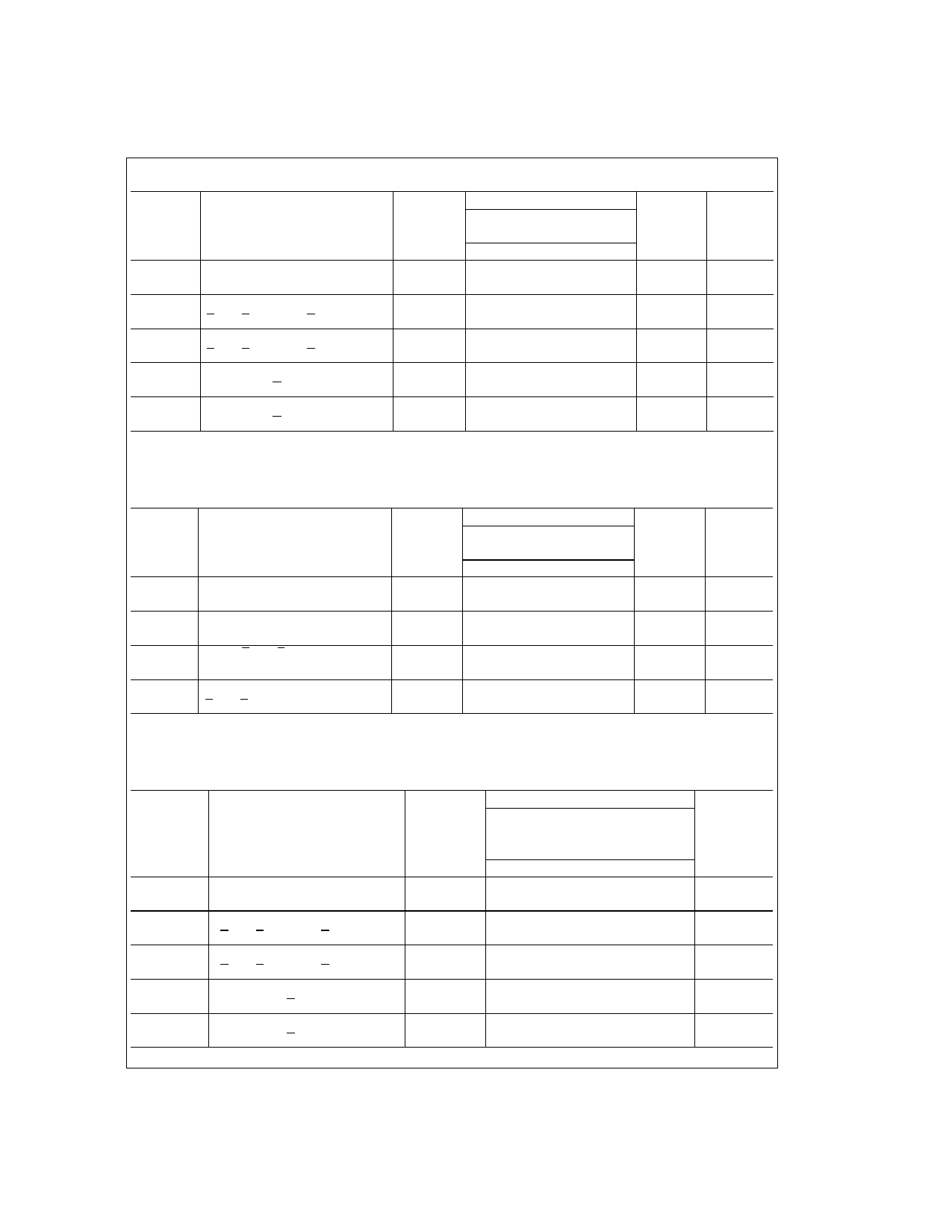

AC Electrical Characteristics

Symbol

Parameter

fmax Maximum Clock

Frequency

tPLH

tPHL

tPLH

tPHL

Propagation Delay

CDn or SDn to Qn or Qn

Propagation Delay

CDn or SDn to Qn or Qn

Propagation Delay

CPn to Qn or Qn

Propagation Delay

CPn to Qn or Qn

Note 8: Voltage Range 3.3 is 3.3V ± 0.3V

Voltage Range 5.0 is 5.0V ± 0.5V

VCC

(V)

(Note 8)

3.3

5.0

3.3

5.0

3.3

5.0

3.3

5.0

3.3

5.0

54AC

TA = −55˚C to +125˚C

CL = 50 pF

Min Max

70

95

1.0 13.0

1.0 9.5

1.0 14.0

1.0 10.5

1.0 17.5

1.0 12.0

1.0 13.5

1.0 10.0

Units

MHz

ns

ns

ns

ns

Fig.

No.

AC Operating Requirements

Symbol

Parameter

ts Set-up Time, HIGH or LOW

Dn to CPn

th Hold Time, HIGH or LOW

Dn to CPn

tw CPn or CDn or SDn

Pulse Width

trec Recovery Time

CDn or SDn to CP

Note 9: Voltage Range 3.3 is 3.3V ±0.3V

Voltage Range 5.0 is 5.0V ±0.5V

VCC

(V)

(Note 9)

3.3

5.0

3.3

5.0

3.3

5.0

3.3

5.0

54AC

TA = −55˚C to +125˚C

CL = 50 pF

Guaranteed Limits

5.0

4.0

0.5

0.5

8.0

5.5

0.5

0.5

Units

ns

ns

ns

ns

Fig.

No.

AC Electrical Characteristics

Symbol

Parameter

fmax Maximum Clock

Frequency

tPLH Propagation Delay

CDn or SDn to Qn or Qn

tPHL Propagation Delay

CDn or SDn to Qn or Qn

tPLH Propagation Delay

CPn to Qn or Qn

tPHL Propagation Delay

CPn to Qn or Qn

VCC

(V)

(Note 10)

5.0

5.0

5.0

5.0

5.0

54ACT

TA = −55˚C

to +125˚C

CL = 50 pF

Min Max

85

1.0 11.5

1.0 12.5

1.0 14.0

1.0 12.0

Units

MHz

ns

ns

ns

ns

5 www.national.com

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet 54AC74.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 54AC74 | Dual D-Type Positive Edge-Triggered Flip-Flop | National Semiconductor |

| 54AC74 | Dual D-Type Positive Edge-Triggered Flip-Flop (Rev. B) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |