|

|

PDF 74HC40105 Data sheet ( Hoja de datos )

| Número de pieza | 74HC40105 | |

| Descripción | 4-bit x 16-word FIFO register | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 74HC40105 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

74HC40105; 74HCT40105

4-bit x 16-word FIFO register

Rev. 4 — 29 January 2016

Product data sheet

1. General description

The 74HC40105; 74HCT40105 is a first-in/first-out (FIFO) "elastic" storage register that

can store 16 4-bit words. It can handle input and output data at different shifting rates.

This feature makes it particularly useful as a buffer between asynchronous systems. Each

word position in the register is clocked by a control flip-flop, which stores a marker bit. A

logic 1 signifies that the data at that position is filled and a logic 0 denotes a vacancy in

that position. The control flip-flop detects the state of the preceding flip-flop and

communicates its own status to the succeeding flip-flop. When a control flip-flop is in the

logic 0 state and sees a logic 1 in the preceding flip-flop, it generates a clock pulse. The

clock pulse transfers data from the preceding four data latches into its own four data

latches and resets the preceding flip-flop to logic 0. The first and last control flip-flops have

buffered outputs. All empty locations "bubble" automatically to the input end, and all valid

data ripples through to the output end. As a result, the status of the first control flip-flop

(data-in ready output - DIR) indicates if the FIFO is full. The status of the last flip-flop

(data-out ready output - DOR) indicates whether the FIFO contains data. As the earliest

data is removed from the bottom of the data stack (output end), all data entered later will

automatically ripple toward the output. Inputs include clamp diodes that enable the use of

current limiting resistors to interface inputs to voltages in excess of VCC.

2. Features and benefits

Independent asynchronous inputs and outputs

Expandable in either direction

Reset capability

Status indicators on inputs and outputs

3-state outputs

Input levels:

For 74HC40105: CMOS level

For 74HCT40105: TTL level

3-state outputs

Complies with JEDEC standard JESD7A

ESD protection:

HBM JESD22-A114F exceeds 2 000 V

MM JESD22-A115-A exceeds 200 V

Multiple package options

Specified from 40 C to +85 C and from 40 C to +125 C

1 page

NXP Semiconductors

74HC40105; 74HCT40105

4-bit x 16-word FIFO register

6. Functional description

6.1 Inputs and outputs

6.1.1 Data inputs (D0 to D3)

As there is no weighting of the inputs, any input can be assigned as the MSB. The size of

the FIFO memory can be reduced from the 4 x 16 configuration. For example, it can be

reduced to 3 x 16, down to 1 x 16, by tying unused data input pins to VCC or GND.

6.1.2 Data outputs (Q0 to Q3)

As there is no weighting of the outputs, any output can be assigned as the MSB. The size

of the FIFO memory can be reduced from the 4 x 16 configuration as described for data

inputs. In a reduced format, the unused data outputs pins must be left open circuit.

6.1.3 Master-reset (MR)

When MR is HIGH, the control functions within the FIFO are cleared, and date content is

declared invalid. The data-in ready (DIR) flag is set HIGH and the data-out-ready (DOR)

flag is set LOW. The output stage remains in the state of the last word that was shifted out,

or in the random state existing at power-up.

6.1.4 Status flag outputs (DIR, DOR)

Two status flags, data-in-ready (DIR) and data-out-ready (DOR), indicate the status of the

FIFO:

1. DIR = HIGH indicates that the input stage is empty and ready to accept valid data;

2. DIR = LOW indicates that the FIFO is full or that a previous shift-in operation is not

complete (busy);

3. DOR = HIGH assures valid data is present at the outputs Q0 to Q3 (does not indicate

that new data is awaiting transfer into the output stage);

4. DOR = LOW indicates that the output stage is busy or there is no valid data.

6.1.5 Shift-in control (SI)

Data is loaded into the input stage on a LOW-to-HIGH transition of SI. It also triggers an

automatic data transfer process (ripple through). If SI is held HIGH during reset, data is

loaded at the falling edge of the MR signal.

6.1.6 Shift-out control (SO)

A HIGH-to-LOW transition of SO causes the DOR flags to go LOW. A HIGH-to-LOW

transition of SO causes upstream data to move into the output stage, and empty locations

to move towards the input stage (bubble-up).

6.1.7 Output enable (OE)

The outputs Q0 to Q3 are enabled when OE = LOW. When OE = HIGH the outputs are in

the high impedance OFF-state.

74HC_HCT40105

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 29 January 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

5 of 36

5 Page

NXP Semiconductors

74HC40105; 74HCT40105

4-bit x 16-word FIFO register

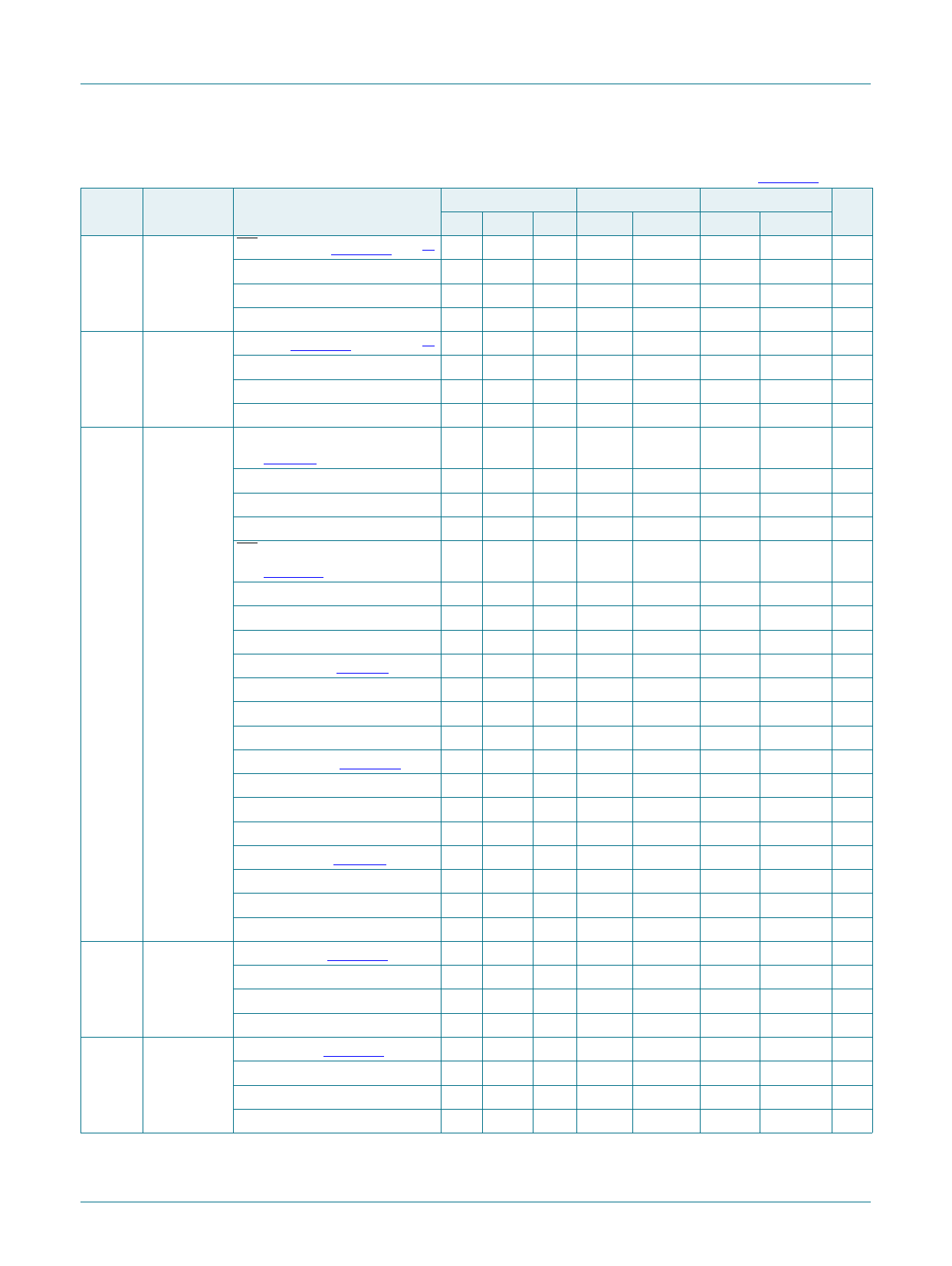

Table 6. Dynamic characteristics …continued

Voltages are referenced to GND (ground = 0 V); CL = 50 pF unless otherwise specified; for test circuit, see Figure 18.

Symbol Parameter Conditions

25 C

40 C to +85 C 40 C to +125 C Unit

Min Typ Max Min Max Min Max

tdis disable time OE to Qn; see Figure 16 [3]

VCC = 2.0 V

- 41 140 -

175

-

210 ns

VCC = 4.5 V

- 15 28

-

35

-

42 ns

VCC = 6.0 V

- 12 24

-

30

-

36 ns

tt transition Qn; see Figure 10

time

VCC = 2.0 V

[4]

- 19 75

-

95

-

110 ns

VCC = 4.5 V

- 7 15 -

19

-

22 ns

VCC = 6.0 V

- 6 13 -

16

-

19 ns

tW pulse width SI HIGH or LOW;

see Figure 8

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

SO HIGH or LOW;

see Figure 11

80 19 - 100

-

120

- ns

16 7 - 20

-

24

- ns

14 6 - 17

-

20

- ns

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

DIR HIGH; see Figure 9

120 39 - 150

-

180

- ns

24 14 - 30

-

36

- ns

20 11 - 26

-

31

- ns

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

DOR LOW; see Figure 14

12 58 180 10

225

10

270 ns

6 21 36

5

45

5

54 ns

5 17 31

4

38

4

46 ns

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

MR HIGH; see Figure 7

12 55 170 10

215

10

255 ns

6 20 34

5

43

5

51 ns

5 16 29

4

37

4

43 ns

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

trec recovery MR to SI; see Figure 15

time

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

tsu set-up time Dn to SI; see Figure 17

VCC = 2.0 V

VCC = 4.5 V

VCC = 6.0 V

80 22 - 100

-

120

- ns

16 8 - 20

-

24

- ns

14 6 - 17

-

20

- ns

50 14 - 65

-

75

- ns

10 5 - 13

-

15

- ns

9 4 - 11

-

13

- ns

5 39 -

5

-

5

- ns

5 14 -

5

-

5

- ns

5 11 -

5

-

5

- ns

74HC_HCT40105

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 29 January 2016

© NXP Semiconductors N.V. 2016. All rights reserved.

11 of 36

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 74HC40105.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74HC40102 | 8-bit synchronous BCD down counter | Philips |

| 74HC40103 | 8-bit synchronous binary down counter | Philips |

| 74HC40103 | 8-bit synchronous binary down counter | NXP Semiconductors |

| 74HC40104 | 4-bit bidirectional universal shift register 3-state | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |