|

|

PDF MAX2306 Data sheet ( Hoja de datos )

| Número de pieza | MAX2306 | |

| Descripción | CDMA IF VGAs and I/Q Demodulators | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX2306 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

19-2014; Rev 3; 8/04

EVALUATION KIT AVAILABLE

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

General Description

The MAX2306/MAX2308/MAX2309 are IF receivers

designed for dual-band, dual-mode, and single-mode

N-CDMA and W-CDMA cellular phone systems. The

signal path consists of a variable-gain amplifier (VGA)

and I/Q demodulator. The devices feature guaranteed

+2.7V operation, a gain control range of over 110dB,

and high input IP3 (-31dBm at 35dB gain, 3.4dBm at

-35dB gain).

Unlike similar devices, the MAX2306 family of receivers

includes dual oscillators and synthesizers to form a

self-contained IF subsystem. The synthesizer’s refer-

ence and RF dividers are fully programmable through a

3-wire serial bus, enabling dual-band system architec-

tures using any common reference and IF frequency.

The differential baseband outputs have enough band-

width to suit both N-CDMA and W-CDMA systems, and

offer saturated output levels of 2.7Vp-p at a low +2.75V

supply voltage. Including the low-noise voltage-con-

trolled oscillator (VCO) and synthesizer, the MAX2306

draws only 26mA from a +2.75V supply in CDMA (dif-

ferential IF) mode.

The MAX2306/MAX2308/MAX2309 are available in 28-

pin Thin QFN and QFN packages.

Applications

Single/Dual/Triple-Mode CDMA Handsets

Globalstar Dual-Mode Handsets

Wireless Data Links

W-CDMA Handsets

Wireless Local Loop (WLL)

Features

♦ Complete IF Subsystem Includes VCO and

Synthesizer

♦ Supports Dual-Band, Triple-Mode Operation

♦ VGA with >110dB Gain Control

♦ Quadrature Demodulator

♦ High Output Level (2.7V)

♦ Programmable Charge-Pump Current

♦ Supports Any IF Frequency Between 40MHz and

300MHz

♦ 3-Wire Programmable Interface

♦ Low Supply Voltage (+2.7V)

PART

MAX2306EGI

MAX2306ETI

MAX2308EGI

MAX2308ETI

MAX2309EGI

MAX2309ETI

*Exposed paddle

Ordering Information

TEMP RANGE

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

-40°C to +85°C

PIN-PACKAGE

28 QFN-EP*

28 TQFN-EP*

28 QFN-EP*

28 TQFN-EP*

28 QFN-EP*

28 TQFN-EP*

Pin Configurations appear at end of data sheet.

Block Diagram appears at end of data sheet.

PART

MAX2306

MAX2308

MAX2309

MODE

AMPS,

Cellular CDMA,

PCS CDMA

AMPS,

Cellular CDMA,

PCS CDMA

External AMPS,

Cellular CDMA,

PCS CDMA

DESCRIPTION

Dual Band, Triple Mode with Two

IF VCOs

Selector Guide

INPUT RANGE

40MHz to 300MHz

Dual Band, Triple Mode with Common

IF VCO

70MHz to 300MHz

Dual Band, Triple Mode (Drives External

AMPS Discriminator)

70MHz to 300MHz

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

1 page

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

Typical Operating Characteristics

(MAX2306/MAX2308/MAX2309 EV kits, VCC = +2.75V, registers set to default power-up states, fIN = 183.7MHz, fREF = 19.2MHz,

synthesizer locked with passive 3rd-order lead-lag loop filter, SHDN = high, VGC set for +35dB voltage gain, differential output load

= 10kΩ, all power levels referred to 50Ω, TA = +25°C, unless otherwise noted.)

RECEIVE SUPPLY CURRENT

vs. SUPPLY VOLTAGE

35.00

32.50

30.00

27.50

TA = +85°C

TA = +25°C

25.00

22.50

TA = -40°C

20.00

2.5

3.0 3.5 4.0 4.5 5.0

SUPPLY VOLTAGE (V)

5.5

GAIN vs. INPUT FREQUENCY

60

55

VGC = 2.5V

50

45

40

35

30

25

20

15

0 100 200 300 400

FREQUENCY (MHz)

500

NOISE FIGURE vs. GAIN

70

60

50

40

30

20

10

0

-40 -30 -20 -10 0 10 20 30 40 50 60 70

GAIN (dB)

RECEIVE SHUTDOWN CURRENT vs.

SUPPLY VOLTAGE

0.014

0.012

0.010

TA = +85°C

0.008

0.006

TA = +25°C

0.004

0.002

TA = -40°C

0

2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

SUPPLY VOLTAGE (V)

GAIN vs. BASEBAND FREQUENCY

60.0

59.5

59.0

58.5

58.0

57.5

57.0

56.5

56.0

0 2 4 6 8 10 12 14 16 18 20

FREQUENCY (MHz)

NOISE FIGURE vs. TEMPERATURE

7.4

GAIN = 50dB

7.2

7.0

6.8

6.6

6.4

6.2

6.0

-40 -20

0 20 40 60

TEMPERATURE (°C)

80 100

GAIN vs. VGC

80

60

40

20

0 TA = +25°C

-20 TA = -40°C

-40

TA = +85°C

-60

-80

0.5

10

0

1.0 1.5 2.0 2.5

VGC (V)

THIRD-ORDER INPUT

INTERCEPT vs. GAIN

TA = -40°C

3.0

-10

TA = +85°C

-20

-30 TA = +25°C

-40

-50

-60

-60 -40 -20 0 20 40 60 80

GAIN (dB)

VCO VOLTAGE vs. TIME

MAX2306/8/9 toc09

SHDN

VCO

VOLTAGE

1V/div

LOCK

LOCK TIME

1.83ms

500µs/div

_______________________________________________________________________________________ 5

5 Page

CDMA IF VGAs and I/Q Demodulators

with VCO and Synthesizer

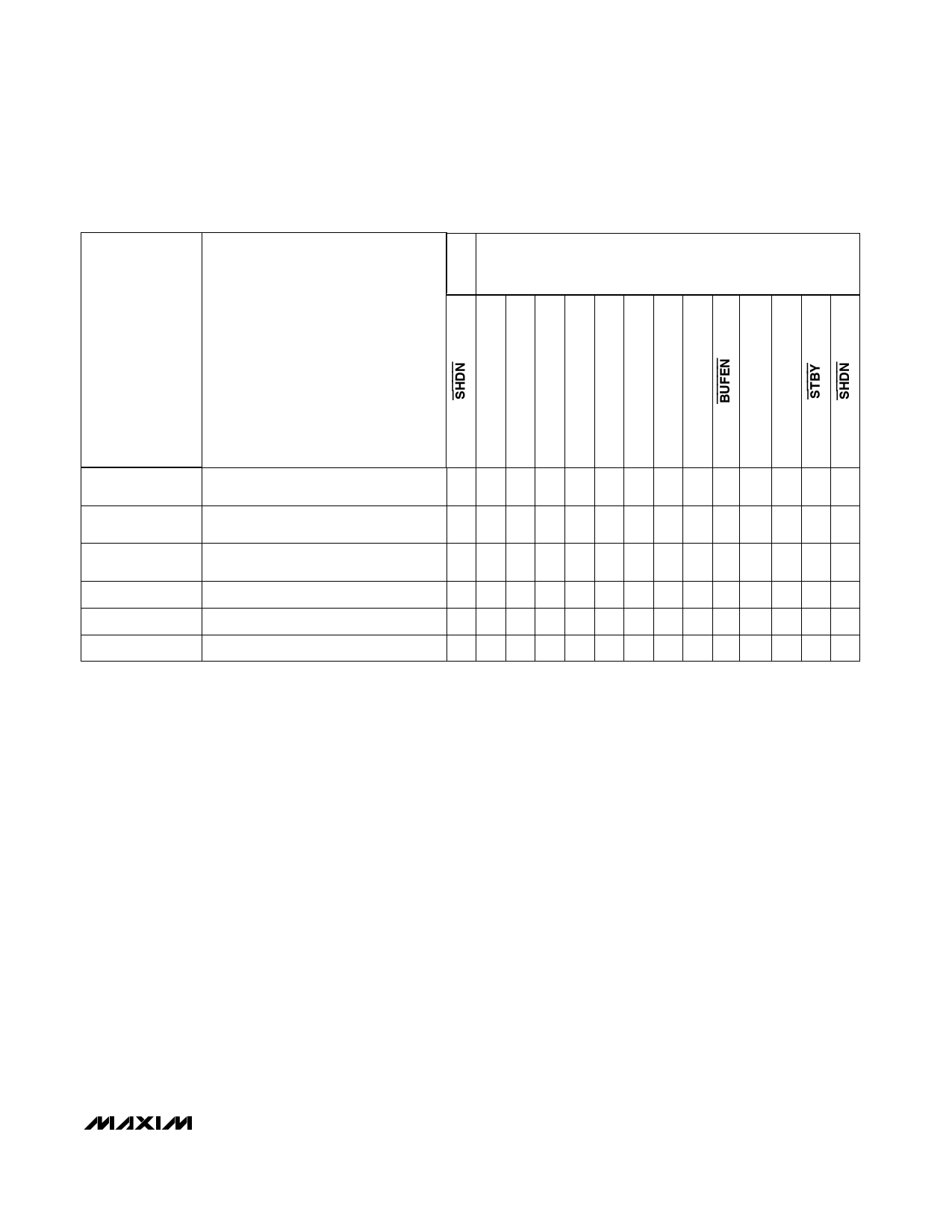

Table 2. MAX2308 Control Register States

PM

IS

NB

M

CONTROLS REGISTER

B

L

S

B

OPERATIONAL

MODE

ACTION

RESULT

SHUTDOWN

SHUTDOWN

STANDBY

Shutdown pin completely shuts down

chip

L

X X X X X X X XX X

XXX

0 in shutdown register bit leaves seri-

al port active

H

X

X

X

X

X

X

X

XX

X

X

X

L

0 in standby pin turns off VGA and

modulator only

H

0

0 XX

01

CDMA

CDMA operation

H0

0 XX X 1 1 1

FM_IQ

FM IQ quadrature operation

H

0

0 XX 0 0 1 1

FM_I

FM I operation

H0

0 XX 1 0 1 1

Note: H = high, L = low, 1 = logic high, 0 = logic low, X = don’t care, blank = independent parameter

When the part initially powers up or changes state, the

synthesizer acquisition time can be reduced by using

the Turbo feature, enabled by the TURBOCHARGE

(TC) control bit. Turbo functionality provides a larger

charge-pump current during acquisition mode. Once

the VCO frequency is acquired, the charge-pump out-

put current magnitude automatically returns to the pre-

programmed state to maintain loop stability and

minimize spurs in the VCO output signal.

The lock detect output indicates when the PLL is

locked with a logic high.

Whenever the M or R divide register value is pro-

grammed and downloaded, the control register must

also be subsequently updated. This prevents turbolock

from going active when not desired.

The SHDN control bit is notable because it differs from

the SHDN pin. When the SHDN control bit is low, the

registers and serial interface are left active, retaining

the values stored in the latches, while the rest of the

device is shut off. In contrast, the SHDN pin, when low,

shuts down everything, including the registers and seri-

al interface. See Functional Diagram.

3-Wire Interface and Registers

The MAX2306 family incorporates a 3-wire interface for

synthesizer programming and device configuration

(Figure 5). The 3-wire interface consists of clock, data,

and enable signals. It controls the VCO dividers (M1

and M2), reference frequency dividers (R1 and R2),

and a 13-bit control register. The control register is

used to set up the operational modes (Table 4). The

input shift is 17 data bits long and requires a total of 18

clock bits (Figure 6). A single clock pulse is required

before enable drops low to initialize the data bus.

Registers

Figure 7 shows the programming logic. The 17-bit shift

register is programmed by clocking in data at the rising

edge of CLK. Before the shift register is able to accept

data, it must be initialized by driving it with at least one

full clock cycle at the CLK input with EN high (see

Figure 6). Pulling enable low will allow data to be

clocked into the shift register; pulling enable high loads

the register addressed by A0, A1, and A2, respectively

(Figure 7). Table 5 lists the power-on default values of

all registers. Table 6 lists the charge-pump current,

depending on CP0 and CP1.

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet MAX2306.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX230 | Multichannel RS-232 Drivers/Receivers | Maxim Integrated |

| MAX2306 | CDMA IF VGAs and I/Q Demodulators | Maxim Integrated |

| MAX2308 | CDMA IF VGAs and I/Q Demodulators | Maxim Integrated |

| MAX2309 | CDMA IF VGAs and I/Q Demodulators | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |