|

|

PDF MC-45D16CB641 Data sheet ( Hoja de datos )

| Número de pieza | MC-45D16CB641 | |

| Descripción | 16 M-WORD BY 64-BIT DDR SYNCHRONOUS DYNAMIC RAM MODULE UNBUFFERED TYPE | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MC-45D16CB641 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

PRELIMINARY DATA SHEET

MOS INTEGRATED CIRCUIT

MC-45D16CB641

16 M-WORD BY 64-BIT DDR SYNCHRONOUS DYNAMIC RAM MODULE

UNBUFFERED TYPE

Description

The MC-45D16CB641 is a 16,777,216 words by 64 bits DDR synchronous dynamic RAM module on which 8 pieces

of 128M DDR SDRAM: µPD45D128842 are assembled.

These modules provide high density and large quantities of memory in a small space without utilizing the surface-

mounting technology on the printed circuit board.

Decoupling capacitors are mounted on power supply line for noise reduction.

Features

• 16,777,216 words by 64 bits organization

• Clock frequency

Part number

/CAS latency

Clock frequency

(MAX.)

Module type

MC-45D16CB641KF-C75

CL = 2.5

133 MHz

DDR SDRAM

CL = 2

100 MHz

Unbuffered DIMM

MC-45D16CB641KF-C80

CL = 2.5

125 MHz

Design specification

CL = 2

100 MHz

Rev.0.9 compliant

• Fully Synchronous Dynamic RAM with all signals except DM, DQS and DQ referenced to a positive clock edge

• Double Data Rate interface

Differential CLK (/CLK) input

Data inputs and DM are synchronized with both edges of DQS

Data outputs and DQS are synchronized with a cross point of CLK and /CLK

• Quad internal banks operation

• Possible to assert random column address in every clock cycle

• Programmable Mode register set

/CAS latency (2, 2.5)

Burst length (2, 4, 8)

Wrap sequence (Sequential / Interleave)

• Automatic precharge and controlled precharge

• CBR (Auto) refresh and self refresh

• 2.5 V ± 0.2 V Power supply for VDD

• 2.5 V ± 0.2 V Power supply for VDDQ

• SSTL_2 compatible with all signals

• 4,096 refresh cycles / 64 ms

• Burst termination by Precharge command and Burst stop command

• 184-pin dual in-line memory module (Pin pitch = 1.27 mm)

• Unbuffered type

• Serial PD

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M14897EJ2V0DS00 (2nd edition)

Date Published June 2000 NS CP(K)

Printed in Japan

The mark 5 shows major revised points.

©

2000

1 page

MC-45D16CB641

Electrical Specifications

• All voltages are referenced to VSS (GND).

• After power up, wait more than 1 ms and then, execute Power on sequence and CBR (auto) refresh before

proper device operation is achieved.

Absolute Maximum Ratings

Parameter

Voltage on power supply pin relative to VSS

Voltage on input pin relative to VSS

Short circuit output current

Power dissipation

Storage temperature

Symbol

VDD, VDDQ

VT

IO

PD

Tstg

Condition

Rating

–0.5 to +3.6

–0.5 to +3.6

50

12

–55 to +125

Unit

V

V

mA

W

°C

Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause

permanent damage. The device is not meant to be operated under conditions outside the limits

described in the operational section of this specification. Exposure to Absolute Maximum Rating

conditions for extended periods may affect device reliability.

Recommended Operating Conditions

Parameter

Symbol

Supply voltage

VDD

Supply voltage for DQ, DQS

VDDQ

Input reference voltage

VREF

Termination voltage

VTT

High level dc input voltage

VIH (DC)

Low level dc input voltage

VIL (DC)

Input differential voltage (CLK and /CLK)

VID (DC)

Input crossing point voltage (CLK and /CLK)

VIX

Operating ambient temperature

TA

Condition

MIN.

2.3

2.3

0.49 × VDDQ

VREF − 0.04

VREF + 0.15

−0.3

0.36

0.5 × VDDQ–0.2

0

TYP.

2.5

2.5

VREF

MAX.

Unit

2.7 V

2.7 V

0.51 × VDDQ

V

VREF + 0.04

V

VDD + 0.3

V

VREF − 0.15

V

VDDQ + 0.6

V

0.5 × VDDQ+0.2

70

V

°C

Capacitance (TA = 25 °C, f = 100 MHz)

Parameter

Input capacitance

Data input/output capacitance

Symbol

Test condition

CI1 A0 - A11, BA0, BA1, /RAS,

/CAS, /WE

CI2 CK0 - CK2, /CK0 - /CK2

CI3 CKE0

CI4 /S0

CI/O1

CI/O2

DM(0-7)/DQS(9-16),

DQS0 - DQS7

DQ0 - DQ63

MIN.

TBD

TYP.

MAX.

TBD

Unit

pF

TBD

TBD

TBD

TBD

TBD

TBD

TBD

TBD

pF

TBD

TBD

Preliminary Data Sheet M14897EJ2V0DS00

5

5 Page

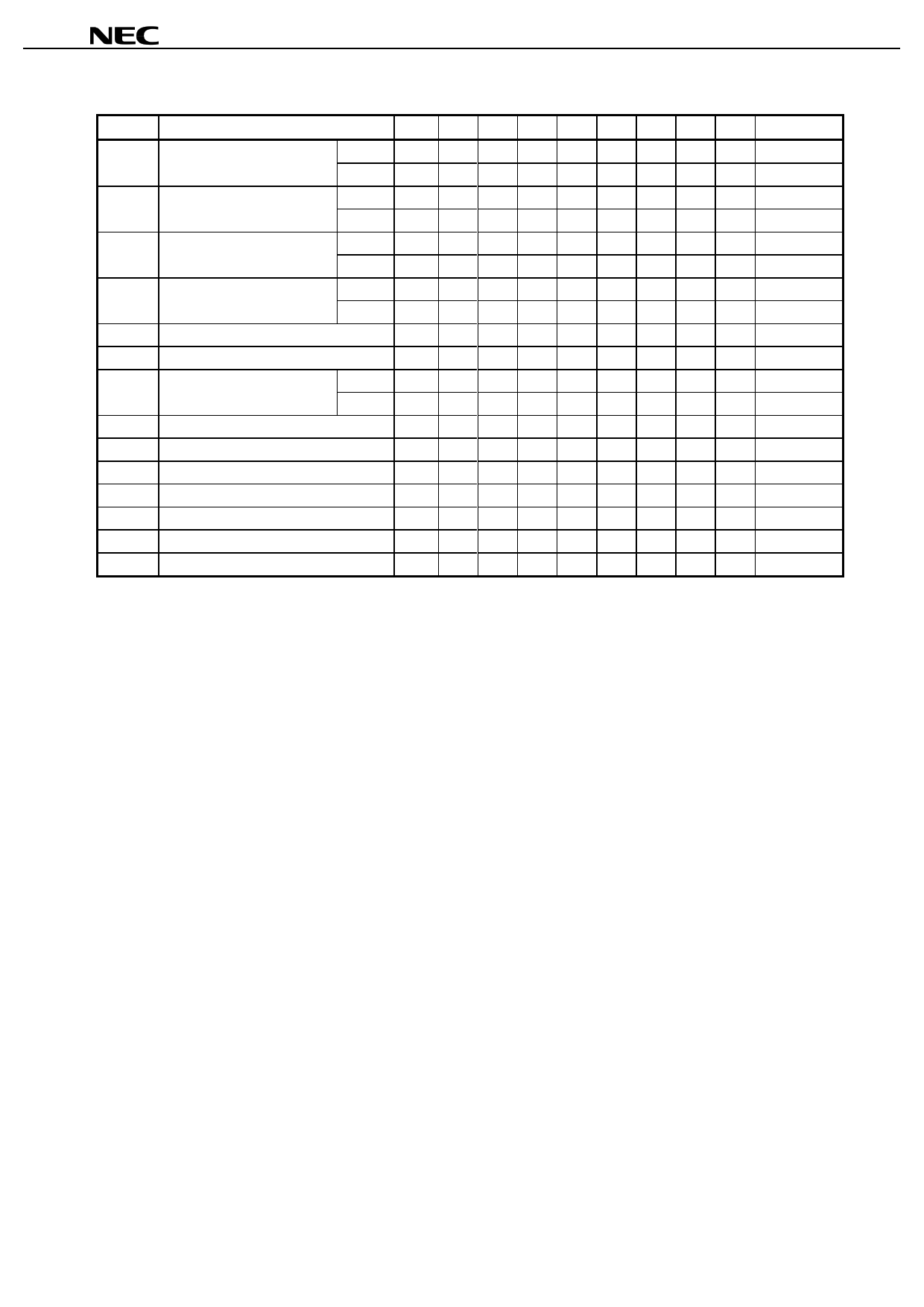

MC-45D16CB641

Byte No.

Function Described

32 Command and address signal

input setup time

33 Command and address signal

input hold time

34 Data signal input setup time

35 Data signal input hold time

36-61

62

63

SPD revision

Checksum for bytes 0 - 62

64-71 Manufacture’s JEDEC ID code

72 Manufacturing location

73-90 Manufacture’s P/N

91 Revision Code

93-94 Manufacturing date

95-99 Assembly serial number

100-127 Mfg specific

-C75

-C80

-C75

-C80

-C75

-C80

-C75

-C80

-C75

-C80

(2/2)

Hex Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0

Notes

90H 1 0 0 1 0 0 0 0 0.9 ns

B0H 1 0 1 1 0 0 0 0 1.1 ns

90H 1 0 0 1 0 0 0 0 0.9 ns

B0H 1 0 1 1 0 0 0 0 1.1 ns

50H 0 1 0 1 0 0 0 0 0.5 ns

60H 0 1 1 0 0 0 0 0 0.6 ns

50H 0 1 0 1 0 0 0 0 0.5 ns

60H 0 1 1 0 0 0 0 0 0.6 ns

00H 0 0 0 0 0 0 0 0

9CH 1 0 0 1 1 1 0 0

22H 0 0 1 0 0 0 1 0

00H 0 0 0 0 0 0 0 0

Timing Chart

Refer to the µPD45D128442, 45D128842, 45D128164 Data sheet (M13852E).

Preliminary Data Sheet M14897EJ2V0DS00

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet MC-45D16CB641.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MC-45D16CB641 | 16 M-WORD BY 64-BIT DDR SYNCHRONOUS DYNAMIC RAM MODULE UNBUFFERED TYPE | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |