|

|

PDF X9241A Data sheet ( Hoja de datos )

| Número de pieza | X9241A | |

| Descripción | Quad Digitally Controlled Potentiometer (XDCP) | |

| Fabricantes | Xicor | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X9241A (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

APPLICATION NOTE

AVAILABLE

AN20 • AN42–48 • AN50-53 • AN73 • AN99 • AN115 • AN120 • AN124 • AN133 • AN134 • AN135

Low Power/2-Wire Serial Bus

X9241A

Quad Digitally Controlled Potentiometer (XDCP™)

FEATURES

• Four potentiometers in one package

• 2-wire serial interface

• Register oriented format

—Direct read/write/transfer of wiper positions

—Store as many as four positions per

potentiometer

• Terminal Voltages: +5V, -3.0V

• Cascade resistor arrays

• Low power CMOS

• High Reliability

—Endurance–100,000 data changes per bit per

register

—Register data retention–100 years

• 16-bytes of nonvolatile memory

• 3 resistor array values

—2KΩ to 50KΩ mask programmable

—Cascadable for values of 500Ω to 200KΩ

• Resolution: 64 taps each pot

• 20-lead plastic DIP, 20-lead TSSOP and 20-lead

SOIC packages

DESCRIPTION

The X9241A integrates four digitally controlled

potentiometers (XDCP) on a monolithic CMOS

integrated microcircuit.

The digitally controlled potentiometer is implemented

using 63 resistive elements in a series array. Between

each element are tap points connected to the wiper

terminal through switches. The position of the wiper on

the array is controlled by the user through the 2-wire

bus interface. Each potentiometer has associated with

it a volatile Wiper Counter Register (WCR) and 4

nonvolatile Data Registers (DR0:DR3) that can be

directly written to and read by the user. The contents

of the WCR controls the position of the wiper on the

resistor array through the switches. Power up recalls

the contents of DR0 to the WCR.

The XDCP can be used as a three-terminal

potentiometer or as a two-terminal variable resistor in

a wide variety of applications including control,

parameter adjustments, and signal processing.

BLOCK DIAGRAM

VCC

VSS

SCL

SDA

A0

A1

A2

A3

Interface

and

Control

Circuitry

8

Data

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

VH0/RH0

VL0/RL0

VW0/RW0

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

Register

Array

Pot 2

VH2/

RH2

VL2/RL2

VW2/RW2

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

Register

Array

Pot 1

VH1/RH1

VL1/RL1

VW1/RW1

R0 R1

R2 R3

Wiper

Counter

Register

(WCR)

Register

Array

Pot 3

VH3/RH3

VL3/RL3

VW3/RW3

REV 1.1.13 12/09/02

www.xicor.com

Characteristics subject to change without notice. 1 of 18

1 page

X9241A

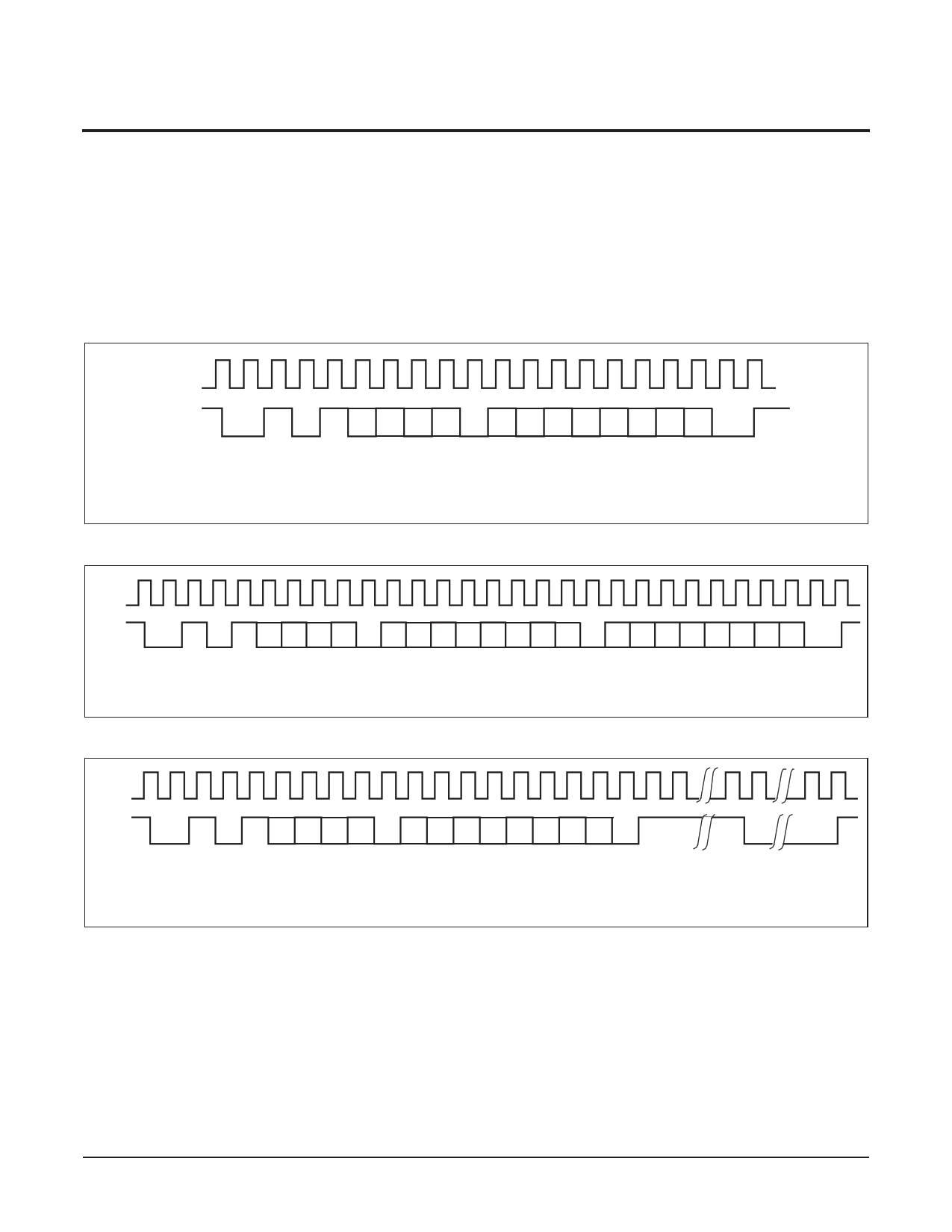

The Increment/Decrement command is different from

the other commands. Once the command is issued and

the X9241A has responded with an acknowledge, the

master can clock the selected wiper up and/or down in

one segment steps; thereby, providing a fine tuning

capability to the host. For each SCL clock pulse (tHIGH)

while SDA is HIGH, the selected wiper will move one

resistor segment towards the VH/RH terminal. Similarly,

for each SCL clock pulse while SDA is LOW, the

selected wiper will move one resistor segment towards

the VL/RL terminal. A detailed illustration of the

sequence and timing for this operation are shown in

Figures 5 and 6 respectively.

Figure 3. Two-Byte Instruction Sequence

SCL

SDA

S 0 1 0 1 A3 A2 A1 A0 A I3 I2 I1 I0 P1 P0 R1 R0 A S

TC

CT

AK

KO

RP

T

Figure 4. Three-Byte Instruction Sequence

SCL

SDA

S 0 1 0 1 A3 A2 A1 A0 A I3 I2 I1 I0 P1 P0 R1 R0 A CM DW D5 D4 D3 D2 D1 D0 A S

TC

C CT

AK

K KO

RP

T

Figure 5. Increment/Decrement Instruction Sequence

SCL

SDA

XX

S 0 1 0 1 A3 A2 A1 A0 A I3 I2 I1 I0 P1 P0 R1 R0 A I I

T C CN N

A K KC C

R 12

T

ID

NE

CC

n1

DS

ET

CO

nP

REV 1.1.13 12/09/02

www.xicor.com

Characteristics subject to change without notice. 5 of 18

5 Page

X9241A

D.C. OPERATING CHARACTERISTICS (Over recommended operating conditions unless otherwise stated.)

Symbol

Parameter

lCC Supply current (active)

ISB VCC current (standby)

ILI Input leakage current

ILO Output leakage current

VIH Input HIGH voltage

VIL Input LOW voltage

VOL Output LOW voltage

Min.

2

–1

Limits

Typ.

Max.

3

200 500

10

10

VCC + 1

0.8

0.4

Unit

mA

µA

µA

µA

V

V

V

Test Condition

fSCL = 100kHz, SDA = Open,

Other Inputs = VSS

SCL = SDA = VCC, Addr. = VSS

VIN = VSS to VCC

VOUT = VSS to VCC

IOL = 3mA

Notes: (1) Absolute Linearity is utilized to determine actual wiper voltage versus expected voltage as determined by wiper position when used

as a potentiometer.

(2) Relative Linearity is utilized to determine the actual change in voltage between two successive tap positions when used as a poten-

tiometer. It is a measure of the error in step size.

(3) MI = RTOT/63 or (RH–RL)/63, single pot

(4) Max. = all four arrays cascaded together, Typical = individual array resolutions.

ENDURANCE AND DATA RETENTION

Parameter

Minimum endurance

Data retention

Min.

100,000

100

Unit

Data changes per bit per register

Years

CAPACITANCE

Symbol

CI/O(5)

CIN(5)

Parameter

Input/output capacitance (SDA)

Input capacitance (A0, A1, A2, A3 and SCL)

Max.

19

12

Unit

pF

pF

Test Condition

VI/O = 0V

VIN = 0V

POWER-UP TIMING

Symbol

tPUR(6)

tPUW(6)

tRVCC

Parameter

Power-up to initiation of read operation

Power-up to initiation of write operation

VCC Power up ramp rate

Min.

0.2

Typ.

Max.

1

5

50

Unit

ms

ms

V/msec

POWER-UP REQUIREMENTS (Power Up sequencing can affect correct recall of the wiper registers)

The preferred power-on sequence is as follows: First Vcc, then the potentiometer pins. It is suggested that Vcc

reach 90% of its final value before power is applied to the potentiometer pins. The Vcc ramp rate specification

should be met, and any glitches or slope changes in the Vcc line should be held to <100mV if possible. Also, Vcc

should not reverse polarity by more than 0.5V.

Notes: (5) This parameter is guaranteed by characterization or sample testing.

(6) tPUR and tPUW are the delays required from the time VCC is stable until the specified operation can be initiated. These parameters

are guaranteed by design.

(7) This parameter is guaranteed by design.

(8) Maximum Wiper Current is derated over temperature. See the Wiper Current Derating Curve.

(9) Ti value denotes the maximum noise glitch pulse width that the device will ignore on either SCL or SDA pins. Any noise glitch pulse

width that is greater than this maximum value will be considered as a valid clock or data pulse and may cause communication failure

to the device.

REV 1.1.13 12/09/02

www.xicor.com

Characteristics subject to change without notice. 11 of 18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet X9241A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X9241 | Quad E2POT Nonvolatile Digital Potentiometer | Xicor |

| X9241A | Quad Digitally Controlled Potentiometer (XDCP) | Xicor |

| X9241A | Quad Digital Controlled Potentionmeters | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |