|

|

PDF ZL30101 Data sheet ( Hoja de datos )

| Número de pieza | ZL30101 | |

| Descripción | T1/E1 Stratum 3 System Synchronizer | |

| Fabricantes | Zarlink Semiconductor Inc | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ZL30101 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ZL30101

T1/E1 Stratum 3 System Synchronizer

Data Sheet

Features

October 2004

• Supports Telcordia GR-1244-CORE Stratum 3

• Supports G.823 and G.824 for 2048 kbit/s and

1544 kbit/s interfaces

• Supports ANSI T1.403 and ETSI ETS 300 011 for

ISDN primary rate interfaces

• Simple hardware control interface

• Accepts two input references and synchronizes to

any combination of 8 kHz, 1.544 MHz, 2.048 MHz,

8.192 MHz or 16.384 MHz inputs

• Provides a range of clock outputs: 1.544 MHz,

2.048 MHz, 16.384 MHz and either 4.096 MHz &

8.192 MHz or 32.768 MHz & 65.536 MHz

• Provides 5 styles of 8 kHz framing pulses

• Holdover frequency accuracy of 1 x 10-8

• Lock, Holdover and Out of Range indication

• Selectable loop filter bandwidth of 1.8 Hz or 922 Hz

• Less than 0.6 nspp jitter on all output clocks

• External master clock source: clock oscillator or

crystal

Ordering Information

ZL30101QDC

64 pin TQFP

-40°C to +85°C

Applications

• Synchronization and timing control for multi-trunk

DS1/E1 systems such as DSLAMs, gateways and

PBXs

• Clock and frame pulse source for ST-BUS, GCI

and other time division multiplex (TDM) buses

REF0

REF1

OSCi OSCo TIE_CLR

BW_SEL LOCK OUT_SEL

Master Clock

MUX

TIE

Corrector

Circuit

Virtual

Reference

DPLL

E1

Synthesizer

REF_FAIL0

REF_FAIL1

REF_SEL

RST

Reference

Monitor

TIE

Corrector

Enable

State Machine

Mode

Control

Feedback

Frequency

Select

MUX

DS1

Synthesizer

IEEE

1149.1a

C2o

C4/C65o

C8/C32o

C16o

F4/F65o

F8/F32o

F16o

C1.5o

TRST

MODE_SEL1:0 HMS HOLDOVER

TCK TDI TMS TDO

Figure 1 - Functional Block Diagram

1

Zarlink Semiconductor Inc.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2004, Zarlink Semiconductor Inc. All Rights Reserved.

1 page

ZL30101

Data Sheet

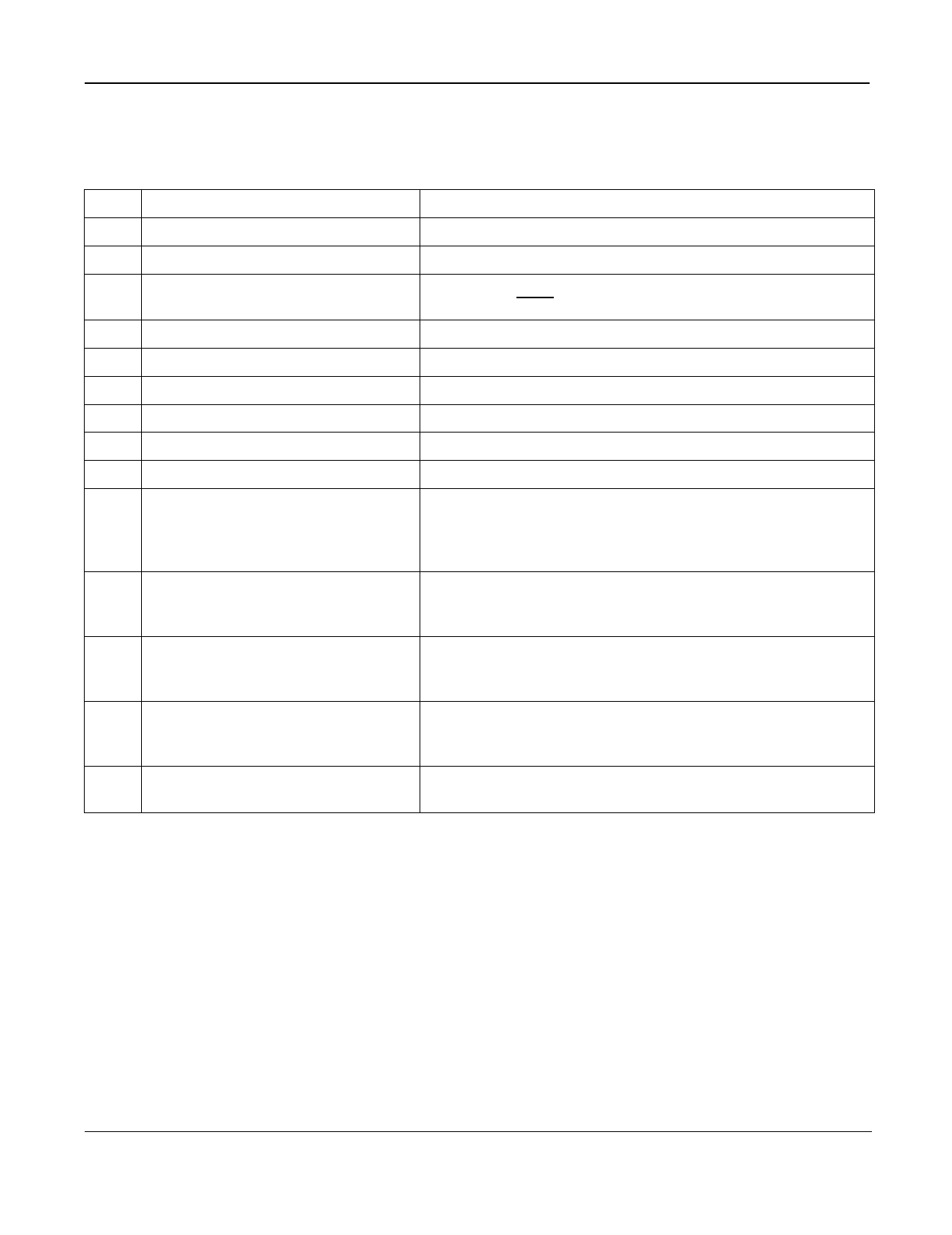

1.0 Change Summary

Changes from June 2004 Issue to October 2004 Issue. Page, section, figure and table numbers refer to this issue.

Page

1

6

7

10

15

19

20

25

26

27

28

32

32

32

Item

Text

Figure 2

Table “Pin Description“

Section 3.2

Section 3.4

Section 4.4

Section 5.0

Section 6.4

Table “Absolute Maximum Ratings*“

Table “DC Electrical Characteristics*“

Table “AC Electrical Characteristics* -

Input Timing for REF0 and REF1

References (see Figure 16)“

Table “Performance Characteristics*:

Output Jitter Generation - ANSI

T1.403 Conformance“

Table “Performance Characteristics*:

Output Jitter Generation - ITU-T

G.812 Conformance“

Table “Performance Characteristics* -

Unfiltered Intrinsic Jitter“

Change

Jitter changed to 0.6 ns from 0.5 ns

Added note specifying not e-Pad

Added information about Schmitt trigger feedback paths to

C1.5o, C2o, C16o, and F8/F32o

Added text about input pulse width restriction

Added details on LOCK pin behaviour

Added text and Figure 10 explaining LOCK pin behaviour

Added Jitter definition

Corrected time-constant of example reset circuit

Corrected package power rating

Corrected current consumption

Corrected input voltage characteristics to reflect Schmitt trigger

Corrected input leakage current to reflect internal pull-ups

Corrected output voltage note to reflect two pad strengths

Added explanatory note

Changed jitter numbers

Changed jitter number

Changed jitter numbers, removed UI column

5

Zarlink Semiconductor Inc.

5 Page

ZL30101

Data Sheet

REF0 /

REF1

Reference Frequency

Detector

Precise Frequency

Monitor

Coarse Frequency

Monitor

Single Cycle

Monitor

REF_FAIL0 /

OR REF_FAIL1

dis/requalify

timer

OR

REF_DIS Mode select

state machine

HOLDOVER

REF_DIS= reference disrupted.

This is an internal signal.

Figure 3 - Reference Monitor Circuit

Exceeding the thresholds of any of the monitors forces the corresponding REF_FAIL pin to go high. The single

cycle and coarse frequency failure flags force the DPLL into Holdover mode and feed a timer that disqualifies the

reference input signal when the failures are present for more than 2.5 s. The single cycle and coarse frequency

failures must be absent for 10 s to let the timer requalify the input reference signal as valid. Multiple failures of less

than 2.5 s each have an accumulative effect and will disqualify the reference eventually. This is illustrated in Figure

4.

SCM or CFM failure

current REF

timer

REF_FAIL

HOLDOVER

2.5 s

10 s

Figure 4 - Behaviour of the Dis/Requalify Timer

When the incoming signal returns to normal (REF_FAIL=0), the DPLL returns to Normal mode with the output

signal locked to the input signal. Each of the monitors has a build-in hysteresis to prevent flickering of the

REF_FAIL status pin at the threshold boundaries. The precise frequency monitor and the timer do not affect the

mode (Holdover/Normal) of the DPLL.

11

Zarlink Semiconductor Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZL30101.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZL30100 | T1/E1 System Synchronizer | Zarlink Semiconductor Inc |

| ZL30101 | T1/E1 Stratum 3 System Synchronizer | Zarlink Semiconductor Inc |

| ZL30102 | T1/E1 Stratum 4/4E Redundant System Clock Synchronizer | Zarlink Semiconductor |

| ZL30105 | T1/E1/SDH Stratum 3 Redundant System Clock Synchronizer | Zarlink Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |