|

|

PDF SI3012 Data sheet ( Hoja de datos )

| Número de pieza | SI3012 | |

| Descripción | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SI3012 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Si3035

3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT

Features

Complete DAA includes the following:

! 3.3 V to 5 V Digital/Analog

Power Supplies

! JATE Filter Option

! 86 dB Dynamic Range TX/RX

Paths

! Daisy-Chaining for Up to Eight

Devices

! Integrated Ring Detector

! 3000 V Isolation

! Support for Caller ID

! Low Profile SOIC Packages

! Direct Interface to DSPs

! Integrated Modem Codec

! Compliant with FCC Part 68

! Low-Power Standby Mode

! Proprietary ISOcap™ Technology

! Pin Compatible with Si3034, Si3032

! Optional IIR Digital Filter

Applications

! V.90 Modems

! Voice Mail Systems

! Fax Machines

! Set Top Boxes

Description

The Si3035 is an integrated direct access arrangement (DAA) chipset that

provides a digital, low-cost, solid-state interface to a telephone line.

Available in two 16-pin small outline packages, it eliminates the need for an

analog front end (AFE), an isolation transformer, relays, opto-isolators, and

a 2- to 4-wire hybrid. The Si3035 dramatically reduces the number of

discrete components and cost required to achieve compliance with FCC

Part 68. The Si3035 interfaces directly to standard modem DSPs and

supports all FCC and JATE out-of-band noise requirements. International

support is provided by the pin compatible Si3034.

Functional Block Diagram

Si3021

Si3012

Ordering Information

See page 50.

Pin Assignments

Si3021 (SOIC)

MCLK

FSYNC

SCLK

VD

SDO

SDI

FC/RGDT

RESET

1

2

3

4

5

6

7

8

16 OFHK

15 RGDT/FSD

14 M0

13 VA

12 GND

11 C1A

10 M1

9 AOUT

Si3021 (TSSOP)

SDO

SDI

FC/RGDT

RESET

AOUT

M1

C1A

GND

1

2

3

4

5

6

7

8

16 VD

15 SCLK

14 FSYNC

13 MCLK

12 OFHK

11 RGDT/FSD

10 M0

9 VA

MCLK

SCLK

FSYNC

SDI

SDO

FC/RGT

RGDT/FSD

OFHK

MODE

RESET

AOUT

Digital

Interface

Isolation

Interface

Control

Interface

Out

Hybrid In

Isolation

Interface

DC

Termination

Ring Detect

Off-Hook

TX

RX

HYBD

VREG2

VREG

DCT

REXT

IGND

RNG1

RNG2

QB

QE

Si3012 (SOIC or TSSOP)

TSTA

TSTB

IGND

C1B

RNG1

RNG2

QB

QE

1

2

3

4

5

6

7

8

16 TX

15 NC

14 RX

13 REXT

12 DCT

11 HYBD

10 VREG2

9 VREG

US Patent # 5,870,046

US Patent # 6,061,009

Other Patents Pending

Rev. 1.2 12/00

Copyright © 2000 by Silicon Laboratories

Si3035-DS12

1 page

Si3035

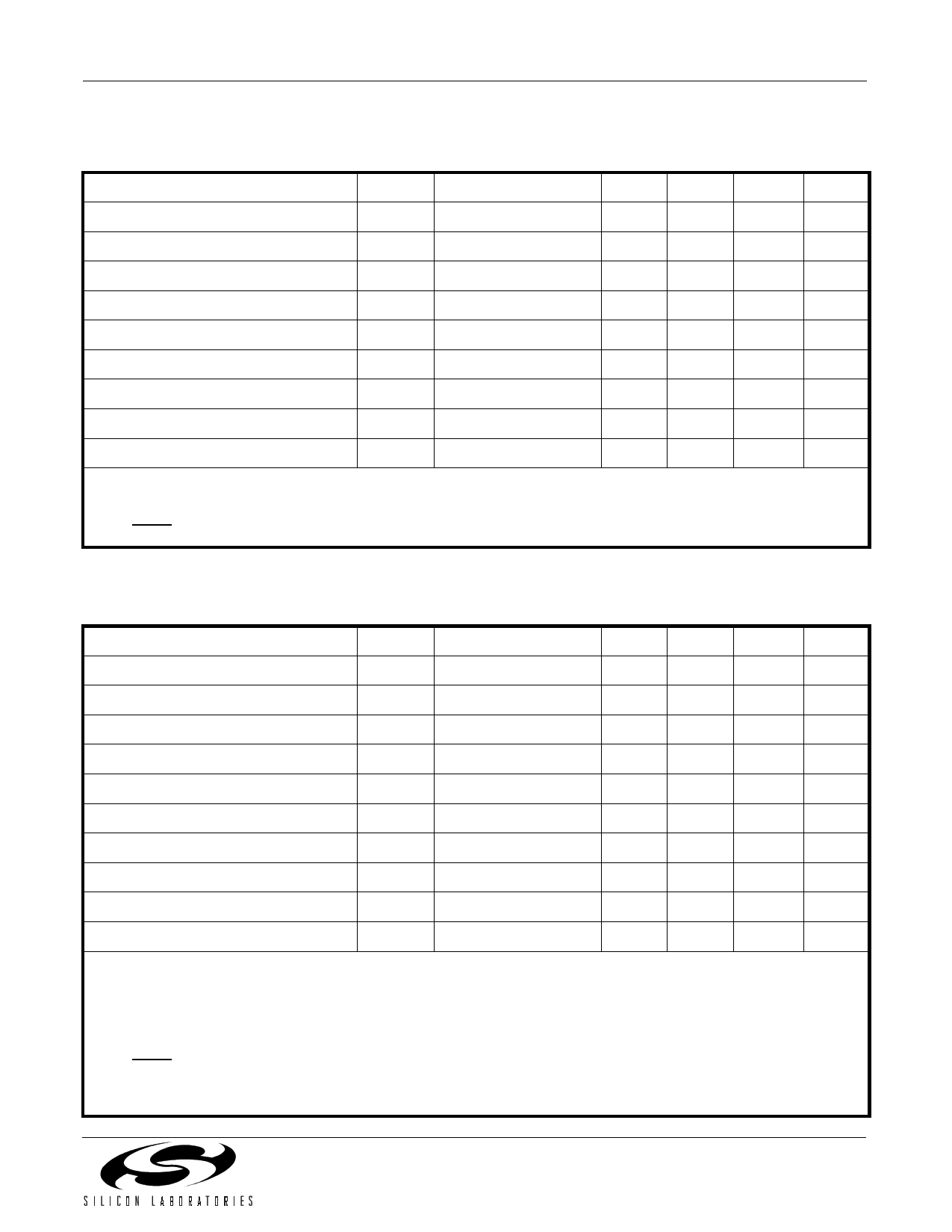

Table 3. DC Characteristics, VD = +5 V

(VA = +5 V ±5%, VD = +5 V ±5%, TA = 0 to 70°C for K-Grade)

Parameter

Symbol

Test Condition

Min Typ Max

High Level Input Voltage

VIH

3.5 —

—

Low Level Input Voltage

VIL

— — 0.8

High Level Output Voltage

VOH

IO = –2 mA

3.5 —

—

Low Level Output Voltage

VOL IO = 2 mA — — 0.4

Input Leakage Current

IL

–10 —

10

Power Supply Current, Analog

IA

VA pin

— 0.3

1

Power Supply Current, Digital1

ID

VD pin

— 14 18

Total Supply Current, Sleep Mode1

IA + ID

PDN = 1, PDL = 0

—

1.3

2.5

Total Supply Current, Deep Sleep1,2

IA + ID

PDN = 1, PDL = 1

—

0.04

0.5

Notes:

1. All inputs at 0.4 or VD – 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded

(Static IOUT = 0 mA).

2. RGDT is not functional in this state.

Unit

V

V

V

V

µA

mA

mA

mA

mA

Table 4. DC Characteristics, VD = +3.3 V

(VA = Charge Pump, VD = +3.3 V ± 0.3 V, TA = 0 to 70°C for K-Grade)

Parameter

Symbol

Test Condition

Min Typ Max Unit

High Level Input Voltage

VIH

2.0 —

—

V

Low Level Input Voltage

VIL

— — 0.8 V

High Level Output Voltage

VOH

IO = –2 mA

2.4 —

—

V

Low Level Output Voltage

VOL IO = 2 mA — — 0.35 V

Input Leakage Current

Power Supply Current, Analog1,2

Power Supply Current, Digital3

Total Supply Current, Sleep Mode3

Total Supply Current, Deep Sleep3,4

Power Supply Voltage, Analog1,5

IL

IA

ID

IA + ID

IA + ID

VA

VA pin

VD pin

PDN = 1, PDL = 0

PDN = 1, PDL = 1

Charge Pump On

–10 —

10

— 0.3

1

— 9 12

— 1.2 2.5

— 0.04 0.5

4.3 4.6 5.00

µA

mA

mA

mA

V

Notes:

1. Only a decoupling capacitor should be connected to VA when the charge pump is on.

2. There is no IA current consumption when the internal charge pump is enabled and only a decoupling cap is connected

to the VA pin.

3. All inputs at 0.4 or VD – 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded

(Static IOUT = 0 mA).

4. RGDT is not functional in this state.

5. The charge pump is recommended to be used only when VD < 4.5 V. When the charge pump is not used, VA should be

applied to the device before VD is applied on power up if driven from separate supplies.

Rev. 1.2

5

5 Page

Si3035

Table 11. Digital FIR Filter Characteristics—Transmit and Receive

(VA = Charge Pump, VD = +5 V ±5%, Sample Rate = 8 kHz, TA = 0 to 70°C for K-Grade)

Parameter

Symbol

Min

Typ

Passband (0.1 dB)

Passband (3 dB)

Passband Ripple Peak-to-Peak

F(0.1 dB)

F(3 dB)

0

0

–0.1

—

—

—

Stopband

— 4.4

Stopband Attenuation

–74 —

Group Delay

tgd — 12/Fs

Note: Typical FIR filter characteristics for Fs = 8000 Hz are shown in Figures 6, 7, 8, and 9.

Max

3.3

3.6

0.1

—

—

—

Unit

kHz

kHz

dB

kHz

dB

sec

Table 12. Digital IIR Filter Characteristics—Transmit and Receive

(VA = Charge Pump, VD = +5 V ±5%, Sample Rate = 8 kHz, TA = 0 to 70°C for K-Grade)

Parameter

Symbol

Min

Typ

Max

Unit

Passband (3 dB)

F(3 dB)

0

— 3.6 kHz

Passband Ripple Peak-to-Peak

–0.2 —

0.2 dB

Stopband

— 4.4 — kHz

Stopband Attenuation

–40 — — dB

Group Delay

tgd

— 1.6/Fs —

sec

Note: Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 10, 11, 12, and 13. Figures 14 and 15 show

group delay versus input frequency.

Rev. 1.2

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SI3012.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SI3010 | GLOBAL SERIAL INTERFACE DIRECT ACCESS ARRANGEMENT | Silicon Laboratories |

| Si3011 | PROGRAMMABLE VOICE DAA SOLUTIONS | Silicon Laboratories |

| SI3012 | 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT | ETC |

| SI3014 | (SI3014/24.38) Global MC97 Silicon DAA | Silicon Laboratories |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |