|

|

PDF K7A801809B Data sheet ( Hoja de datos )

| Número de pieza | K7A801809B | |

| Descripción | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K7A801809B (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

K7A803601M

K7A801801M

256Kx36 & 512Kx18 Synchronous SRAM

Document Title

256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM

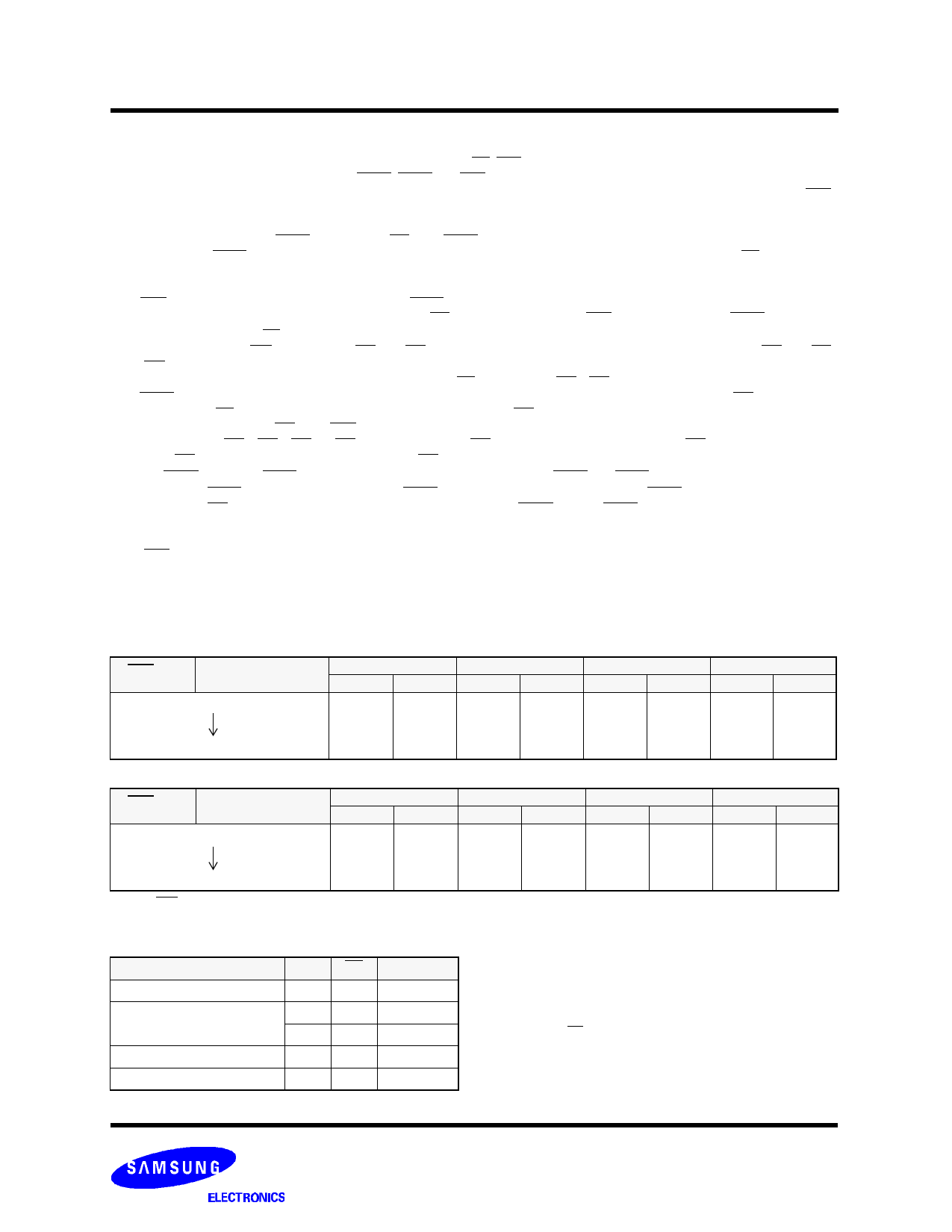

Revision History

Rev. No. History

0.0 Initial draft

0.1 Modify DC characteristics( Input Leakage Current test Conditions)

form VDD=VSS to VDD to Max.

0.2 Remove 119BGA Package Type.

0.3 Change DC Characteristics.

ISB value from 65mA to 110mA at -72

ISB value from 60mA to 110mA at -85

ISB value from 50mA to 100mA at -10

ISB1 value from 10mA to 30mA

ISB2 value from 10mA to 30mA

0.4 1. Changed tCD from 4.0ns to 4.2ns at -85.

Changed tOE from 4.0ns to 4.2ns at -85.

2. Changed DC condition at Icc and parameters

Icc ; from 375mA to 400mA at -72,

from 340mA to 380mA at -85,

from 300mA to 350mA at -10,

ISB ; from 110mA to 130mA at -72,

from 110mA to 130mA at -85,

from 100mA to 120mA at -10

0.5 ADD VDDQ Supply voltage( 2.5V )

0.6 Changed VOL Max value from 0.2V to 0.4V at 2.5V I/O.

1.0 Final spec Release.

2.0 1. Remove VDDQ Supply voltage( 2.5V I/O )

3.0 1. Add VDDQ Supply voltage( 2.5V I/O )

Draft Date

Remark

May. 07 . 1998 Preliminary

June .08. 1998 Preliminary

Aug. 20. 1998 Preliminary

Aug. 27. 1998 Preliminary

Sep. 09. 1998 Preliminary

Dec. 10. 1998

Dec. 23. 1998

Jan. 29. 1999

Feb. 25. 1999

May. 13. 1999

Preliminary

Preliminary

Final

Final

Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

- 1 - May 1999

Rev 3.0

1 page

K7A803601M

K7A801801M

256Kx36 & 512Kx18 Synchronous SRAM

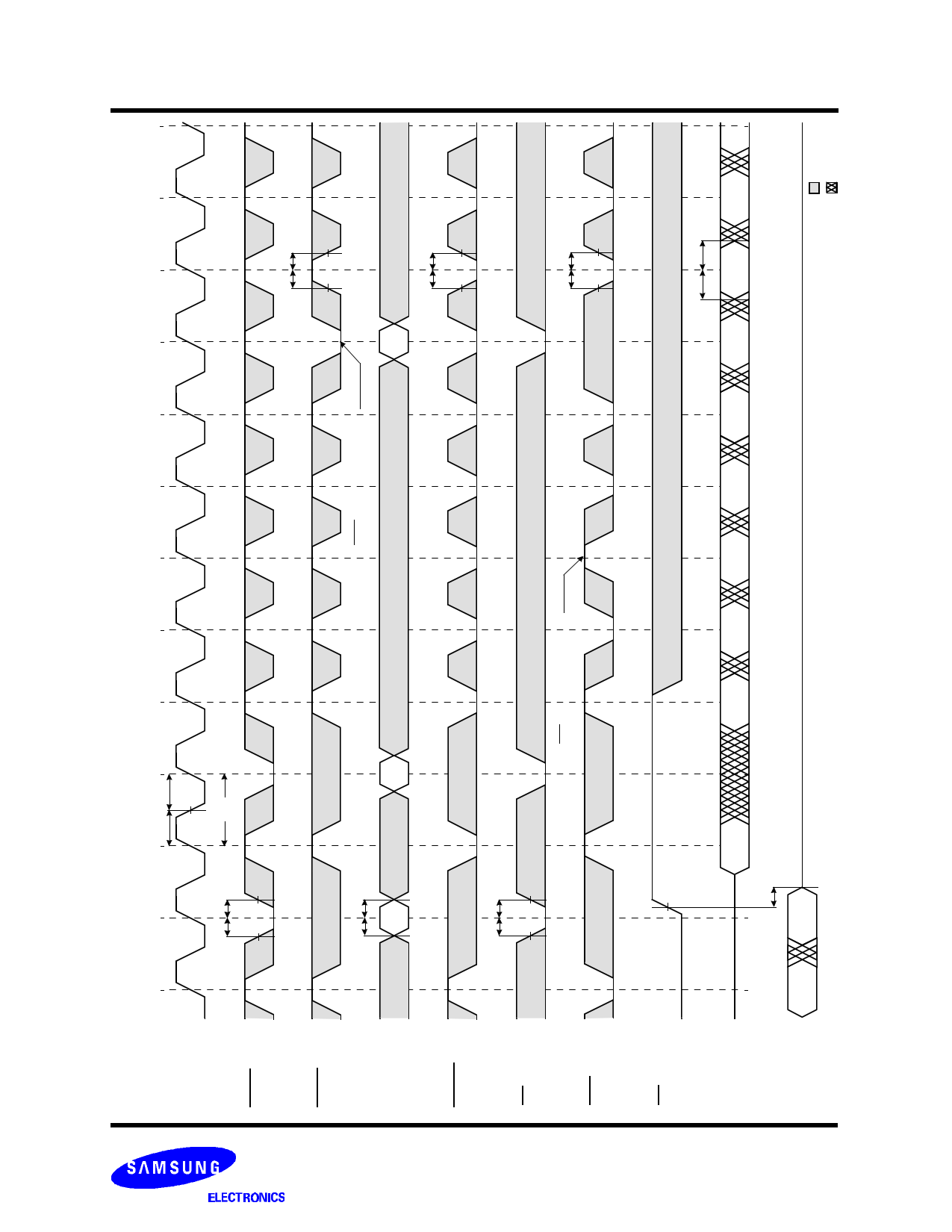

FUNCTION DESCRIPTION

The K7A803601M and K7A801801M are synchronous SRAM designed to support the burst address accessing sequence of the

Power PC based microprocessor. All inputs (with the exception of OE, LBO and ZZ) are sampled on rising clock edges. The start and

duration of the burst access is controlled by ADSC, ADSP and ADV and chip select pins.

The accesses are enabled with the chip select signals and output enabled signals. Wait states are inserted into the access with ADV.

When ZZ is pulled high, the SRAM will enter a Power Down State. At this time, internal state of the SRAM is preserved. When ZZ

returns to low, the SRAM normally operates after 2cycles of wake up time. ZZ pin is pulled down internally.

Read cycles are initiated with ADSP(regardless of WEx and ADSC)using the new external address clocked into the on-chip address

register whenever ADSP is sampled low, the chip selects are sampled active, and the output buffer is enabled with OE. In read oper-

ation the data of cell array accessed by the current address, registered in the Data-out registers by the positive edge of CLK, are car-

ried to the Data-out buffer by the next positive edge of CLK. The data, registered in the Data-out buffer, are projected to the output

pins. ADV is ignored on the clock edge that samples ADSP asserted, but is sampled on the subsequent clock edges. The address

increases internally for the next access of the burst when WEx are sampled High and ADV is sampled low. And ADSP is blocked to

control signals by disabling CS1.

All byte write is done by GW(regaedless of BW and WEx.), and each byte write is performed by the combination of BW and WEx

when GW is high.

Write cycles are performed by disabling the output buffers with OE and asserting WEx. WEx are ignored on the clock edge that sam-

ples ADSP low, but are sampled on the subsequent clock edges. The output buffers are disabled when WEx are sampled

Low(regaedless of OE). Data is clocked into the data input register when WEx sampled Low. The address increases internally to the

next address of burst, if both WEx and ADV are sampled Low. Individual byte write cycles are performed by any one or more byte

write enable signals(WEa, WEb, WEc or WEd) sampled low. The WEa control DQa0 ~ DQa7 and DQPa, WEb controls DQb0 ~ DQb7

and DQPb, WEc controls DQc0 ~ DQc7 and DQPc, and WEd control DQd0 ~ DQd7 and DQPd. Read or write cycle may also be initi-

ated with ADSC, instead of ADSP. The differences between cycles initiated with ADSC and ADSP as are follows;

ADSP must be sampled high when ADSC is sampled low to initiate a cycle with ADSC.

WEx are sampled on the same clock edge that sampled ADSC low(and ADSP high).

Addresses are generated for the burst access as shown below, The starting point of the burst sequence is provided by the external

address. The burst address counter wraps around to its initial state upon completion. The burst sequence is determined by the state

of the LBO pin. When this pin is Low, linear burst sequence is selected. When this pin is High, Interleaved burst sequence is selected.

BURST SEQUENCE TABLE

LBO PIN

HIGH

First Address

Fourth Address

Case 1

A1 A0

00

01

10

11

Case 2

A1 A0

01

00

11

10

BQ TABLE

LBO PIN

LOW

First Address

Fourth Address

Case 1

A1 A0

00

01

10

11

Case 2

A1 A0

01

10

11

00

Note : 1. LBO pin must be tied to High or Low, and Floating State must not be allowed.

Case 3

A1 A0

10

11

00

01

Case 3

A1 A0

10

11

00

01

(Interleaved Burst)

Case 4

A1 A0

11

10

01

00

(Linear Burst)

Case 4

A1 A0

11

00

01

10

ASYNCHRONOUS TRUTH TABLE

OPERATION

Sleep Mode

Read

ZZ OE I/O Status

HX

High-Z

LL

DQ

LH

High-Z

Write

Deselected

L X Din, High-Z

LX

High-Z

Notes

1. X means "Don′t Care".

2. ZZ pin is pulled down internally

3. For write cycles that following read cycles, the output buffers must be

disabled with OE, otherwise data bus contention will occur.

4. Sleep Mode means power down state of which stand-by current does

not depend on cycle time.

5. Deselected means power down state of which stand-by current

depends on cycle time.

- 5 - May 1999

Rev 3.0

5 Page

K7A803601M

K7A801801M

256Kx36 & 512Kx18 Synchronous SRAM

- 11 -

May 1999

Rev 3.0

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet K7A801809B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K7A801809A | 256Kx36 & 512Kx18 Synchronous SRAM | Samsung semiconductor |

| K7A801809B | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM | Samsung semiconductor |

| K7A801809B-QC25 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM | Samsung semiconductor |

| K7A801809B-QCI25 | 256Kx36 & 512Kx18-Bit Synchronous Pipelined Burst SRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |