|

|

PDF K6E0808C1C-15 Data sheet ( Hoja de datos )

| Número de pieza | K6E0808C1C-15 | |

| Descripción | 32Kx8 Bit High Speed CMOS Static RAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K6E0808C1C-15 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

K6E0808C1C-C

PRELIMINARY

CMOS SRAM

Document Title

32Kx8 Bit High Speed Static RAM(5V Operating), Evolutionary Pin out.

Revision History

RevNo. History

Rev. 0.0 Initial release with Preliminary.

Rev. 1.0

Release to final Data Sheet.

1. Delete Preliminary

Rev. 2.0

Update A.C parameters

2.1. Updated A.C parameters

Items

Previous spec.

(12/15/20ns part)

Updated spec.

(12/15/20ns part)

tOE

- / 8/10ns

- / 7 /9 ns

tCW

- /12/ - ns

- /11/ - ns

tHZ

8/10/10ns

6/ 7/10ns

tOHZ

- / 8 / - ns

- / 7 / - ns

tDW

- / 9 / - ns

- / 8 / - ns

2.2. Add VOH1=3.95V with the test condition as Vcc=5V±5% at 25°C

Rev. 3.0

3.1. Add 28-TSOP1 Package.

3.2. Add L-version.

3.3. Add Data Rentention Characteristics.

Rev. 4.0

4.1. Delete DIP Package.

4.2. Delete L-version.

4.3. Delete Data Retention Characteristics and Waveform.

Draft Data

Apr. 1st, 1994

May 14th,1994

Remark

Preliminary

Final

Oct. 4th, 1994

Final

Feb. 22th, 1996 Final

Feb. 25th, 1998 Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

-1-

Rev 4.0

February 1998

1 page

K6E0808C1C-C

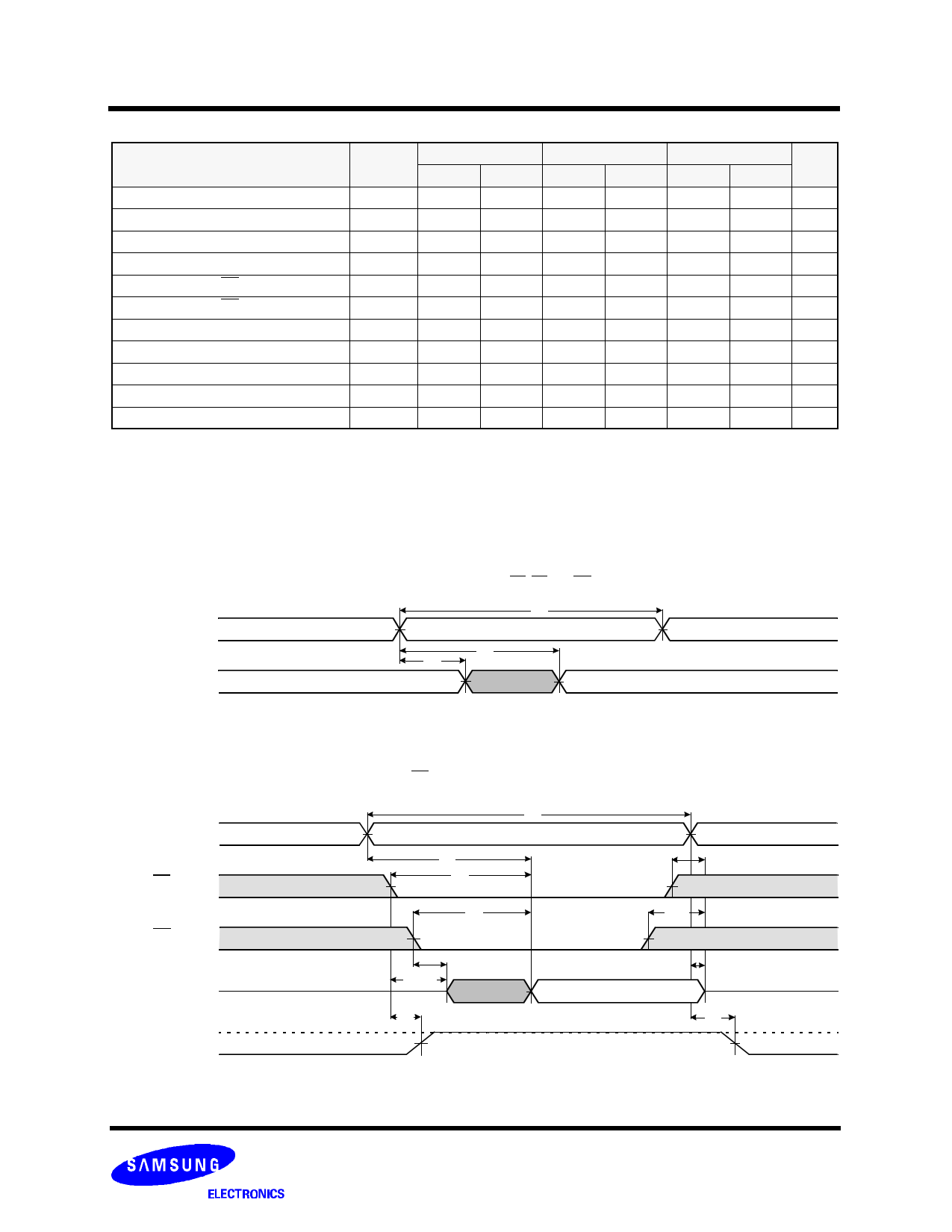

WRITE CYCLE

Parameter

Write Cycle Time

Chip Select to End of Write

Address Setup Time

Address Valid to End of Write

Write Pulse Width(OE High)

Write Pulse Width(OE Low)

Write Recovery Time

Write to Output High-Z

Data to Write Time Overlap

Data Hold from Write Time

End Write to Output Low-Z

PRELIMINARY

CMOS SRAM

Symbol

tWC

tCW

tAS

tAW

tWP

tWP1

tWR

tWHZ

tDW

tDH

tOW

K6E0808C1C-12

Min Max

12 -

9-

0-

9-

9-

12 -

0-

06

7-

0-

0-

K6E0808C1C-15

Min Max

15 -

11 -

0-

12 -

12 -

15 -

0-

08

8-

0-

0-

K6E0808C1C-20

Min Max

20 -

13 -

0-

13 -

13 -

20 -

0-

08

10 -

0-

0-

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TIMMING DIAGRAMS

TIMING WAVEFORM OF READ CYCLE(1) (Address Controlled, CS=OE=VIL, WE=VIH)

Address

Data Out

tOH

Previous Valid Data

tAA

tRC

Valid Data

TIMING WAVEFORM OF READ CYCLE(2) (WE=VIH)

Address

CS

OE

Data out

VCC

Current

ICC

ISB

tAA

tCO

tOE

tOLZ

tLZ(4,5)

tPU

50%

tRC

tHZ(3,4,5)

tOHZ

Valid Data

tOH

tPD

50%

-5-

Rev 4.0

February 1998

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet K6E0808C1C-15.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K6E0808C1C-12 | 32Kx8 Bit High Speed CMOS Static RAM | Samsung semiconductor |

| K6E0808C1C-15 | 32Kx8 Bit High Speed CMOS Static RAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |