|

|

PDF IDT71128S20YI Data sheet ( Hoja de datos )

| Número de pieza | IDT71128S20YI | |

| Descripción | CMOS Static RAM 1 Meg (256K x 4-Bit) Revolutionary Pinout | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT71128S20YI (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

CMOS Static RAM

1 Meg (256K x 4-Bit)

Revolutionary Pinout

IDT71128

Features

x 256K x 4 advanced high-speed CMOS static RAM

x JEDEC revolutionary pinout (center power/GND) for

reduced noise.

x Equal access and cycle times

— Commercial and Industrial: 12/15/20ns

x One Chip Select plus one Output Enable pin

x Bidirectional inputs and outputs directly

TTL-compatible

x Low power consumption via chip deselect

x Available in a 32-pin 400 mil Plastic SOJ.

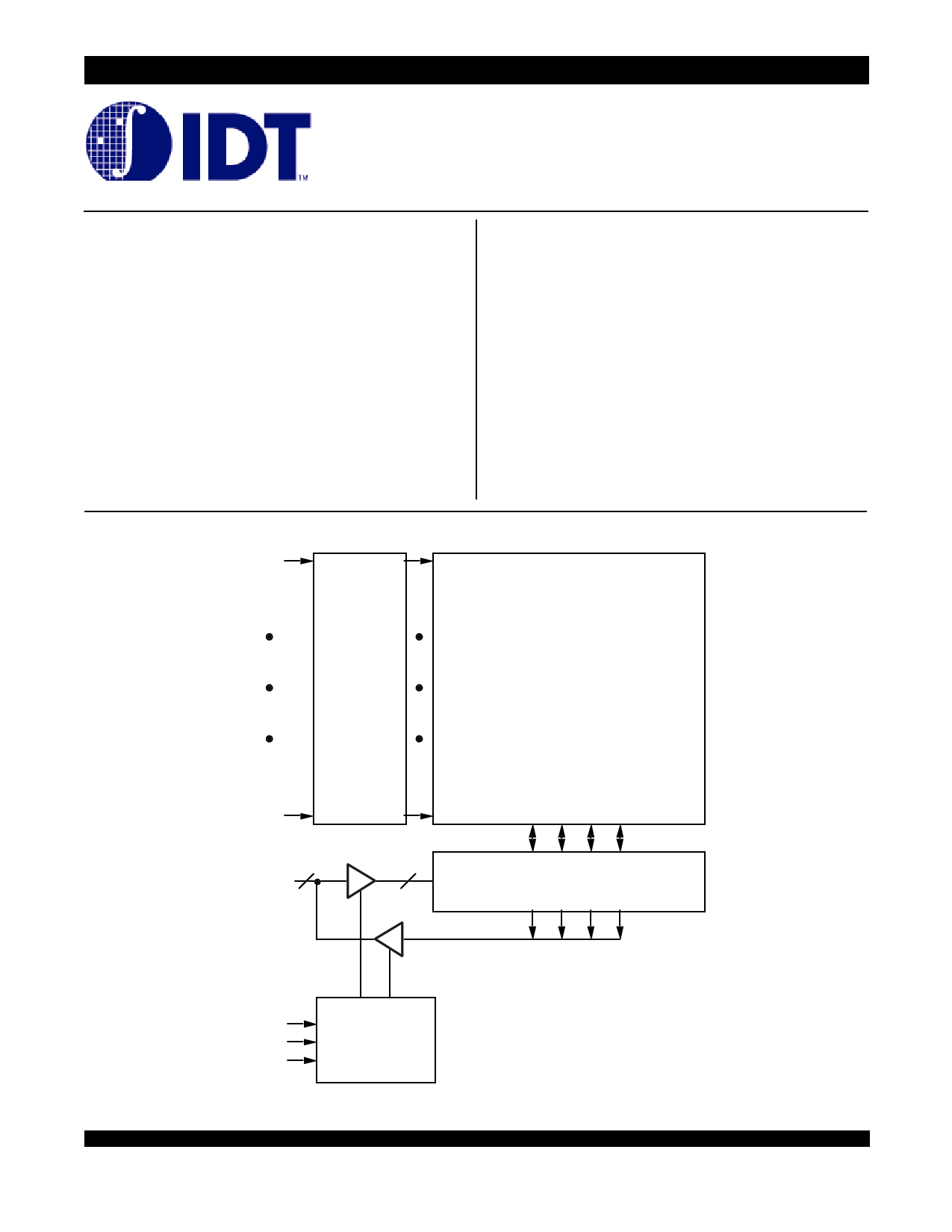

Functional Block Diagram

A0

Description

The IDT71128 is a 1,048,576-bit high-speed static RAM

organized as 256K x 4. It is fabricated using IDT’s high-perfor-

mance, high-reliability CMOS technology. This state-of-the-art

technology, combined with innovative circuit design techniques,

provides a cost-effective solution for high-speed memory needs.

The JEDEC centerpower/GND pinout reduces noise generation

and improves system performance.

The IDT71128 has an output enable pin which operates as fast

as 6ns, with address access times as fast as 12ns available. All

bidirectional inputs and outputs of the IDT71128 are TTL-compat-

ible and operation is from a single 5V supply. Fully static asyn-

chronous circuitry is used; no clocks or refreshes are required for

operation.

The IDT71128 is packaged in a 32-pin 400 mil Plastic SOJ.

ADDRESS

DECODER

A17

4

I/O0 - I/O3

4

1,048,576-BIT

MEMORY

ARRAY

I/O CONTROL

.

CS

WE

OE

CONTROL

LOGIC

©2000 Integrated Device Technology, Inc.

1

3483 drw 01

FEBRUARY 2001

DSC-3483/09

1 page

IDT 71128 CMOS Static RAM

1 Meg (256K x 4-bit) Revolutionary Pinout

Timing Waveform of Read Cycle No. 1(1)

ADDRESS

OE

CS

DATAOUT

tRC

tAA

tOE

tOLZ (5)

tCLZ (5)

tACS (3)

HIGH IMPEDANCE

VCC SUPPLY ICC

CURRENT ISB

tPU

Commercial and Industrial Temperature Ranges

tOHZ (5)

tCHZ (5)

DATAOUT VALID

tPD

3483 drw 05

Timing Waveform of Read Cycle No. 2 (1, 2, 4)

ADDRESS

DATAOUT

tRC

tOH

PREVIOUS DATAOUT VALID

tAA

tOH

DATAOUT VALID

NOTES:

1. WE is HIGH for Read Cycle.

2. Device is continuously selected,CS is LOW.

3. Address must be valid prior to or coincident with the later of CS transition LOW; otherwise tAA is the limiting parameter.

4. OE isLOW.

5. Transition is measured ±200mV from steady state.

3483 drw 06

6.452

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet IDT71128S20YI.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT71128S20Y | CMOS Static RAM 1 Meg (256K x 4-Bit) Revolutionary Pinout | Integrated Device Technology |

| IDT71128S20YI | CMOS Static RAM 1 Meg (256K x 4-Bit) Revolutionary Pinout | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |