|

|

PDF ADE7758 Data sheet ( Hoja de datos )

| Número de pieza | ADE7758 | |

| Descripción | Poly Phase Multifunction Energy Metering IC with Per Phase Information | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADE7758 (archivo pdf) en la parte inferior de esta página. Total 68 Páginas | ||

|

No Preview Available !

Poly Phase Multifunction Energy Metering IC

with Per Phase Information

ADE7758

FEATURES

High accuracy, supports IEC 60687, IEC 61036, IEC 61268,

IEC 62053-21, IEC 62053-22, and IEC 62053-23

Compatible with 3-phase/3-wire, 3-phase/4-wire, and other

3-phase services

Less than 0.1% active energy error over a dynamic range of

1000 to 1 at 25°C

Supplies active/reactive/apparent energy, voltage rms,

current rms, and sampled waveform data

Two pulse outputs, one for active power and the other

selectable between reactive and apparent power with

programmable frequency

Digital power, phase, and rms offset calibration

On-chip user programmable thresholds for line voltage SAG

and overvoltage detections

On-chip digital integrator enables direct interface-to-current

sensors with di/dt output

A PGA in the current channel allows direct interface to

shunts and current transformers

A SPI® compatible serial interface with IRQ

Proprietary ADCs and DSP provide high accuracy over large

variations in environmental conditions and time

Reference 2.4 V (drift 30 ppm/°C typ) with external

overdrive capability

Single 5 V supply, low power (70 mW typ)

GENERAL DESCRIPTION

The ADE77581 is a high accuracy 3-phase electrical energy

measurement IC with a serial interface and two pulse outputs.

The ADE7758 incorporates second-order ∑-∆ ADCs, a digital

integrator, reference circuitry, temperature sensor, and all the

signal processing required to perform active, reactive, and

apparent energy measurement and rms calculations.

The ADE7758 is suitable to measure active, reactive, and

apparent energy in various 3-phase configurations, such as

WYE or DELTA services, both with three or four wires. The

ADE7758 provides system calibration features for each phase,

i.e., rms offset correction, phase calibration, and power

calibration. The APCF logic output gives active power

information, and the VARCF logic output provides

instantaneous reactive or apparent power information.

(Continued on Page 4)

AVDD

4

REFIN/OUT

12

AGND

11

FUNCTIONAL BLOCK DIAGRAM

IAP 5

IAN 6

VAP 16

IBP 7

IBN 8

VBP 15

ICP 9

ICN 10

VCP 14

VN 13

POWER

SUPPLY

MONITOR

2.4V

REF

4kΩ

PGA1

+

–

ADC

PGA2

+

–

ADC

PGA1

+

–

PGA1

+

–

ADC

PGA2

+

–

ADC

ADC

PGA2

+

–

ADC

X2

AVRMSGAIN[11:0]

AVRMSOS[11:0]

AVAG[11:0]

X2

AIGAIN[11:0]

HPF

90° PHASE

SHIFTING FILTER

π

dt 2

INTEGRATOR

AIRMSOS[11:0]

LPF

LPF2

AVAROS[11:0] AVARG[11:0]

Φ

APHCAL[6:0]

LPF2

AWATTOS[11:0] AWG[11:0]

ACTIVE/REACTIVE/APPARENT ENERGIES

AND VOLTAGE/CURRENT RMS CALCULATION

FOR PHASE B

(SEE PHASE A FOR DETAILED SIGNAL PATH)

ACTIVE/REACTIVE/APPARENT ENERGIES

AND VOLTAGE/CURRENT RMS CALCULATION

FOR PHASE C

(SEE PHASE A FOR DETAILED SIGNAL PATH)

VADIV[7:0]

VARDIV[7:0]

WDIV[7:0]

%

%

%

ADE7758 REGISTERS AND

SERIAL INTERFACE

ADE7758

REACTIVE OR

APPARENT POWER

VARCFNUM[11:0]

DFC ÷

17 VARCF

VARCFDEN[11:0]

PHASE B

AND

PHASE C

DATA

ACTIVE POWER

APCFNUM[11:0]

DFC ÷

APCFDEN[11:0]

1 APCF

3 DVDD

2 DGND

19 CLKIN

20 CLKOUT

22 24 23

DIN DOUT SCLK

21

CS

18

IRQ

1 Patents Pending.

Figure 1.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

1 page

ADE7758

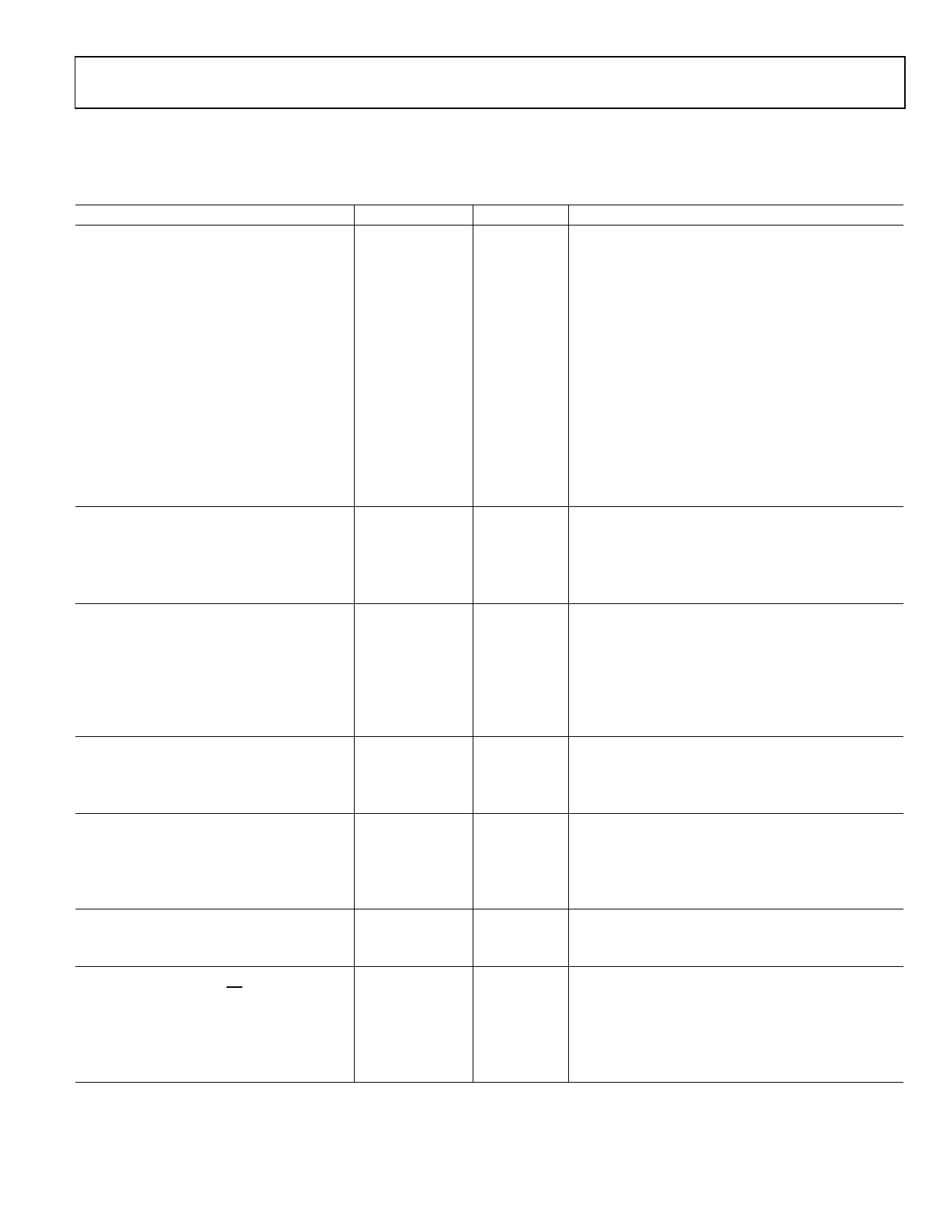

SPECIFICATIONS1, 2

AVDD = DVDD = 5 V ± 5%, AGND = DGND = 0 V, on-chip reference, CLKIN = 10 MHz XTAL, TMIN to TMAX = −40°C to +85°C.

Table 1.

Parameter

ACCURACY

Active Energy Measurement Error

(per Phase)

Phase Error between Channels

(PF = 0.8 Capacitive)

(PF = 0.5 Inductive)

AC Power Supply Rejection1

Output Frequency Variation

DC Power Supply Rejection1

Output Frequency Variation

Active Power Measurement Bandwidth

IRMS Measurement Error

IRMS Measurement Bandwidth

VRMS Measurement Error

VRMS Measurement Bandwidth

ANALOG INPUTS

Maximum Signal Levels

Input Impedance (DC)

ADC Offset Error3

Gain Error1, 3

WAVEFORM SAMPLING

Current Channels

Signal-to-Noise Plus Distortion

Bandwidth (−3 dB)

Voltage Channels

Signal-to-Noise Plus Distortion

Bandwidth (−3 dB)

REFERENCE INPUT

REFIN/OUT Input Voltage Range

Input Capacitance

ON-CHIP REFERENCE

Reference Error

Current Source

Output Impedance

Temperature Coefficient

CLKIN

Input Clock Frequency

LOGIC INPUTS

DIN, SCLK, CLKIN, and CS

Input High Voltage, VINH

Input Low Voltage, VINL

Input Current, IIN

Input Capacitance, CIN

Specification

0.1

±0.05

±0.05

0.01

0.01

14

0.5

14

0.5

260

±500

380

30

±6

62

14

62

180

2.7

2.3

10

±200

6

4

30

15

5

Unit Test Conditions/Comments

% typ

°max

°max

% typ

% typ

kHz

% typ

kHz

% typ

Hz

mV max

kΩ min

mV max

% typ

dB typ

kHz

dB typ

Hz

Over a dynamic range of 1000 to 1

Line frequency = 45 Hz to 65 Hz, HPF on

Phase lead 37°

Phase lag 60°

AVDD = DVDD = 5 V + 175 mV rms/120 Hz

V1P = V2P = V3P = 100 mV rms

AVDD = DVDD = 5 V ± 250 mV dc

V1P = V2P = V3P = 100 mV rms

Over a dynamic range of 500:1

Over a dynamic range of 20:1

See the Analog Inputs section

Differential input

Uncalibrated error, see the Terminology section

External 2.5 V reference

Sampling CLKIN/128, 10 MHz/128 = 78.1 kSPS

See the Current Channel ADC section

See the Voltage Channel ADC section

V max

V min

pF max

mV max

µA max

kΩ min

ppm/°C typ

MHz max

MHz min

2.5 V + 8%

2.5 V – 8%

Nominal 2.4 V at REFIN/OUT pin

All specifications CLKIN of 10 MHz

2.4

V min

DVDD = 5 V ± 5%

0.8

V max

DVDD = 5 V ± 5%

±3

µA max

Typical 10 nA, VIN = 0 V to DVDD

10 pF max

Rev. A | Page 5 of 68

5 Page

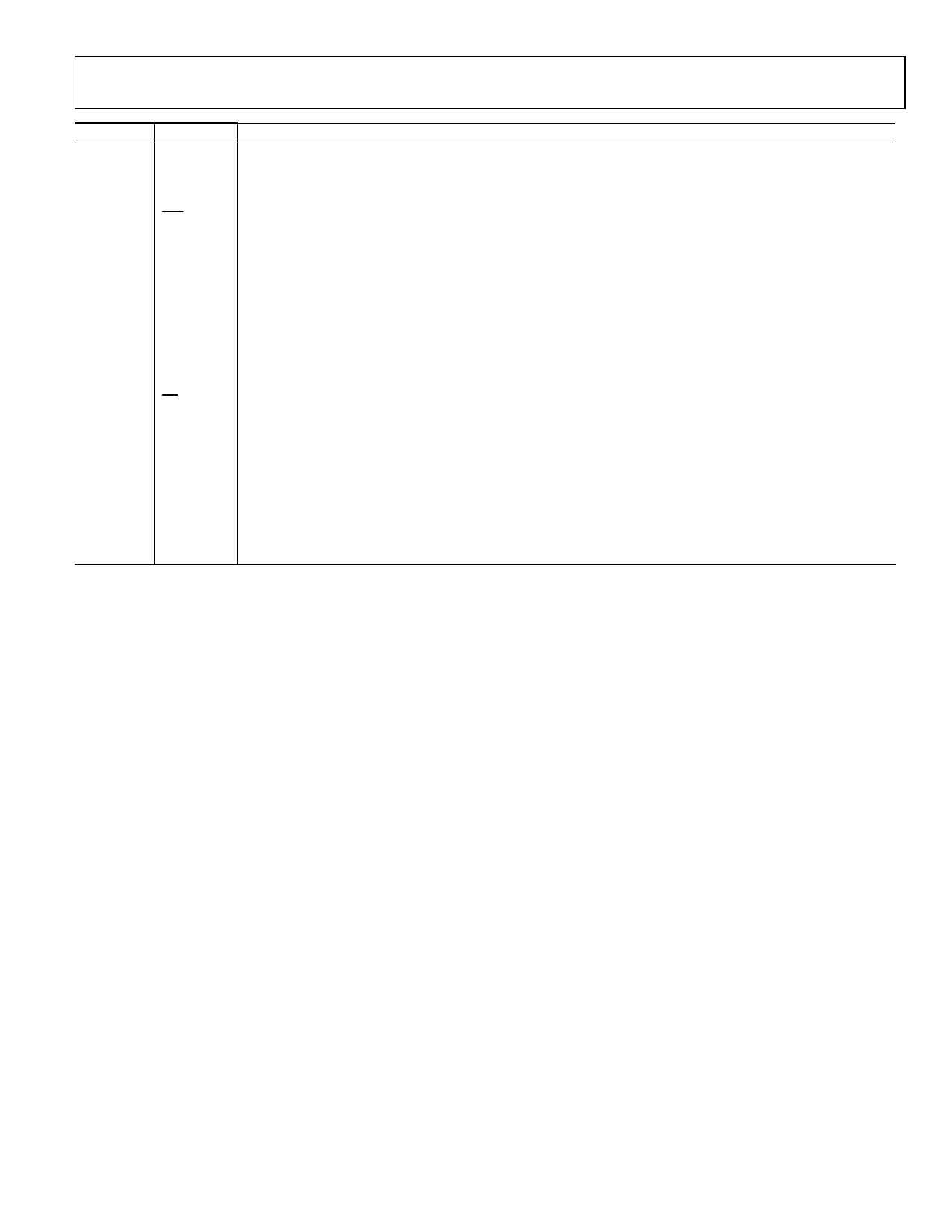

ADE7758

Pin No.

17

18

19

20

21

22

23

24

Mnemonic

VARCF

IRQ

CLKIN

CLKOUT

CS

DIN

SCLK

DOUT

Description

Reactive Power Calibration Frequency Logic Output. It gives reactive power or apparent power information

depending on the setting of the VACF bit of the WAVMODE register. This output is used for operational and

calibration purposes. The full-scale output frequency can be scaled by writing to the VARCFNUM and

VARCFDEN registers (see the Reactive Power Frequency Output section).

Interrupt Request Output. This is an active low open-drain logic output. Maskable interrupts include: active

energy register at half level, apparent energy register at half level, and waveform sampling up to 26 kSPS (see

the ADE7758 Interrupts section).

Master Clock for ADCs and Digital Signal Processing. An external clock can be provided at this logic input.

Alternatively, a parallel resonant AT crystal can be connected across CLKIN and CLKOUT to provide a clock

source for the ADE7758. The clock frequency for specified operation is 10 MHz. Ceramic load capacitors of a

few tens of picofarad should be used with the gate oscillator circuit. Refer to the crystal manufacturer’s data

sheet for the load capacitance requirements

A crystal can be connected across this pin and CLKIN as previously described to provide a clock source for the

ADE7758. The CLKOUT pin can drive one CMOS load when either an external clock is supplied at CLKIN or a

crystal is being used.

Chip Select. Part of the 4-wire serial interface. This active low logic input allows the ADE7758 to share the serial

bus with several other devices (see the ADE7758 Serial Interface section).

Data Input for the Serial Interface. Data is shifted in at this pin on the falling edge of SCLK (see the ADE7758

Serial Interface section).

Serial Clock Input for the Synchronous Serial Interface. All serial data transfers are synchronized to this clock

(see the ADE7758 Serial Interface section). The SCLK has a Schmidt-trigger input for use with a clock source

which has a slow edge transition time, for example, opto-isolator outputs.

Data Output for the Serial Interface. Data is shifted out at this pin on the rising edge of SCLK. This logic output

is normally in a high impedance state, unless it is driving data onto the serial data bus (see the ADE7758 Serial

Interface section).

Rev. A | Page 11 of 68

11 Page | ||

| Páginas | Total 68 Páginas | |

| PDF Descargar | [ Datasheet ADE7758.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADE7751 | Energy Metering IC with On-Chip Fault Detection | Analog Devices |

| ADE7751AAN-REF | Energy Metering IC with On-Chip Fault Detection | Analog Devices |

| ADE7751AN | Energy Metering IC with On-Chip Fault Detection | Analog Devices |

| ADE7751ARS | Energy Metering IC with On-Chip Fault Detection | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |