|

|

PDF MPC9774 Data sheet ( Hoja de datos )

| Número de pieza | MPC9774 | |

| Descripción | LVCMOS PLL CLOCK GENERATOR | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MPC9774 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Order Number: MPC9774/D

Rev 1, 04/2002

Product Preview

3.3V/2.5V 1:14 LVCMOS PLL

Clock Generator

The MPC9774 is a 3.3V or 2.5V compatible, 1:14 PLL based clock

generator targeted for high performance low-skew clock distribution in

mid-range to high-performance networking, computing and telecom

applications. With output frequencies up to 125 MHz and output skews

less than 300 ps1 the device meets the needs of the most demanding

clock applications.

Features

• 1:14 PLL based low-voltage clock generator

• 2.5V or 3.3V power supply

• Internal power–on reset

• Generates clock signals up to 125 MHz

• Maximum output skew of 300 ps1

• Two LVCMOS PLL reference clock inputs

• External PLL feedback supports zero-delay capability

• Various feedback and output dividers (see application section)

• Supports up to three individual generated output clock frequencies

• Drives up to 28 clock lines

• Ambient temperature range 0°C to +85°C

• Pin and function compatible to the MPC974

MPC9774

3.3V/2.5V 1:14 LVCMOS

PLL CLOCK GENERATOR

FA SUFFIX

52 LEAD LQFP PACKAGE

CASE 848D

Functional Description

The MPC9774 utilizes PLL technology to frequency lock its outputs onto an input reference clock. Normal operation of the

MPC9774 requires the connection of the PLL feedback output QFB to feedback input FB_IN to close the PLL feedback path. The

reference clock frequency and the divider for the feedback path determine the VCO frequency. Both must be selected to match

the VCO frequency range.

The MPC9774 features frequency programmability between the three output banks outputs as well as the output to input

relationships. Output frequency ratios of 1:1, 2:1, 3:1, 3:2 and 3:2:1 can be realized. Additionally, the device supports a separate

configurable feedback output which allows for a wide variety of of input/output frequency multiplication alternatives. The

VCO_SEL pin provides an extended PLL input reference frequency range.

The REF_SEL pin selects the internal crystal oscillator or the LVCMOS compatible inputs as the reference clock signal. Two

alternative LVCMOS compatible clock inputs are provided for clock redundancy support. The PLL_EN control selects the PLL

bypass configuration for test and diagnosis. In this configuration, the selected input reference clock is routed directly to the output

dividers bypassing the PLL. The PLL bypass is fully static and the minimum clock frequency specification and all other PLL

characteristics do not apply.

The MPC9774 has an internal power–on reset.

The MPC9774 is fully 2.5V and 3.3V compatible and requires no external loop filter components. All inputs (except XTAL)

accept LVCMOS signals while the outputs provide LVCMOS compatible levels with the capability to drive terminated 50 Ω

transmission lines. For series terminated transmission lines, each of the MPC9774 outputs can drive one or two traces giving the

devices an effective fanout of 1:12. The device is pin and function compatible to the MPC974 and is packaged in a 52-lead LQFP

package.

1. Final specification of this parameter is pending characterization.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

© Motorola, Inc. 2002

1

1 page

MPC9774

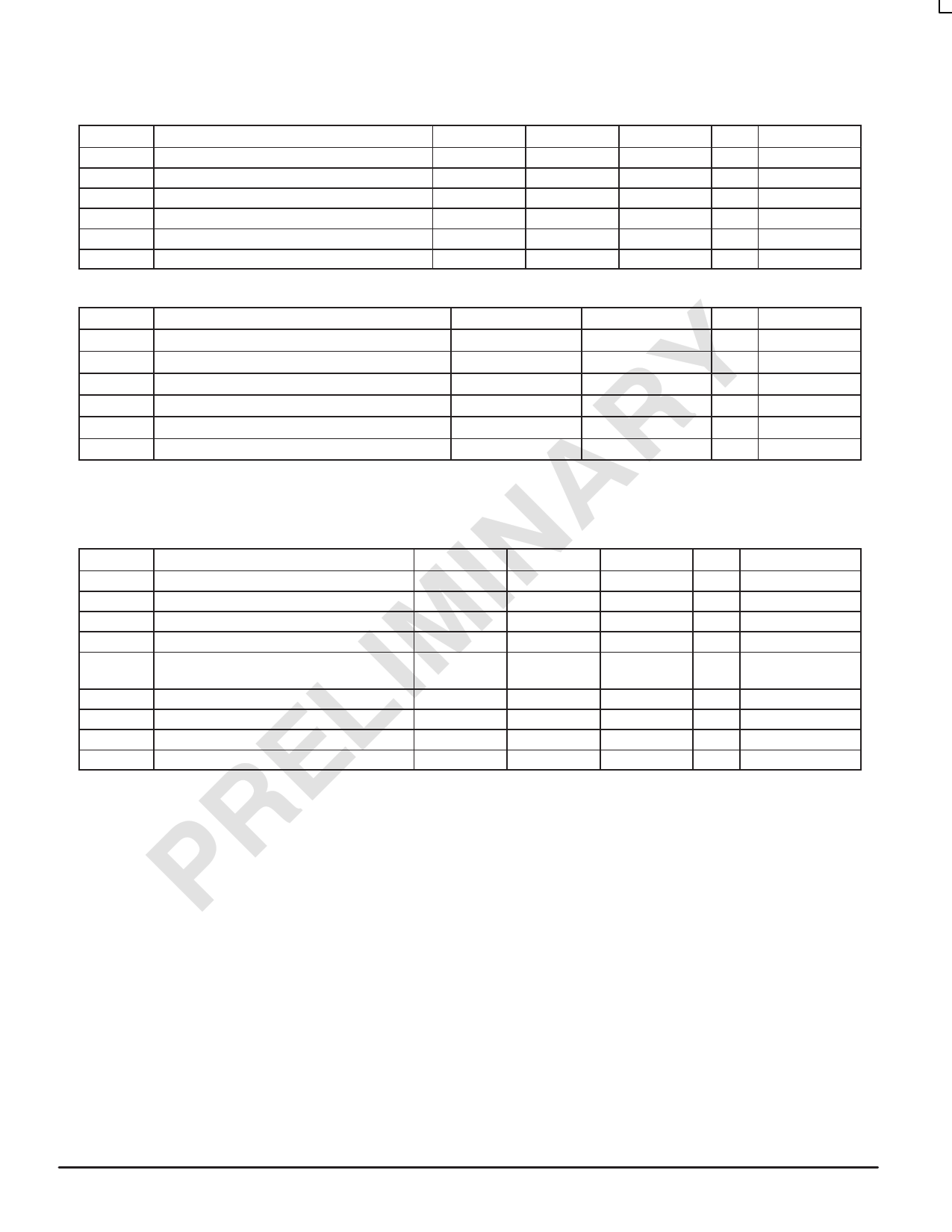

Table 5. General Specifications

Symbol

Characteristics

VTT

MM

HBM

Output termination voltage

ESD protection (Machine model)

ESD protection (Human body model)

LU Latch-up immunity

CPD

CIN

Power dissipation capacitance

Input capacitance

Min

200

2000

200

Typ

VCC ÷ 2

12

4.0

Max Unit Condition

V

V

V

mA

pF Per output

pF Inputs

Table 6. Absolute Maximum Ratingsa

Symbol

Characteristics

Min Max Unit Condition5

VCC

Supply Voltage

-0.3 3.6 V

VIN DC Input Voltage

-0.3

VCC + 0.3

V

VOUT

DC Output Voltage

-0.3

VCC + 0.3

V

IIN DC Input Current

±20 mA

IOUT

DC Output Current

±50 mA

TS Storage temperature

-65 125 °C

a. Absolute maximum continuous ratings are those maximum values beyond which damage to the device may occur. Exposure to these

conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation at absolute-maximum-rated

conditions is not implied.

Table 7. DC Characteristics (VCC = 3.3V ± 5%, TA = 0°C to +85°C)

Symbol

Characteristics

Min Typ Max Unit Condition

VCC_PLL PLL supply voltage

2.325

VCC

V LVCMOS

VIH Input high voltage

2.0

VCC + 0.3

V LVCMOS

VIL

VOH

Input low voltage

Output High Voltage

0.8 V LVCMOS

2.4 V IOH = -24 mAa

VOL

Output Low Voltage

0.55 V IOL = 24 mA

0.30 V IOL = 12 mA

ZOUT

IIN

Output impedance

Input Currentb

14 - 17

±200

Ω

µA VIN = VCC or GND

ICC_PLL Maximum PLL Supply Current

3.0 5.0 mA VCC_PLL Pin

ICCQ

Maximum Quiescent Supply Current

1.0 mA All VCC Pins

a. The MPC9774 is capable of driving 50Ω transmission lines on the incident edge. Each output drives one 50Ω parallel terminated

transmission line to a termination voltage of VTT. Alternatively, the device drives up to two 50Ω series terminated transmission lines.

b. Inputs have pull-down or pull-up resistors affecting the input current.

TIMING SOLUTIONS

5

MOTOROLA

5 Page

MPC9774

Power Supply Filtering

The MPC9774 is a mixed analog/digital product. Its analog

circuitry is naturally susceptible to random noise, especially if

this noise is seen on the power supply pins. Random noise

on the VCC_PLL power supply impacts the device

characteristics, for instance I/O jitter. The MPC9774 provides

separate power supplies for the output buffers (VCC) and the

phase-locked loop (VCC_PLL) of the device.The purpose of

this design technique is to isolate the high switching noise

digital outputs from the relatively sensitive internal analog

phase-locked loop. In a digital system environment where it

is more difficult to minimize noise on the power supplies a

second level of isolation may be required. The simple but

effective form of isolation is a power supply filter on the

VCC_PLL pin for the MPC9774. Figure 10 illustrates a typical

power supply filter scheme. The MPC9774 frequency and

phase stability is most susceptible to noise with spectral

content in the 100 kHz to 20 MHz range. Therefore the filter

should be designed to target this range. The key parameter

that needs to be met in the final filter design is the DC voltage

drop across the series filter resistor RF. From the data sheet

the ICC_PLL current (the current sourced through the

VCC_PLL pin) is typically 3 mA (5 mA maximum), assuming

that a minimum of 2.325V (VCC = 3.3V or VCC = 2.5V) must

be maintained on the VCC_PLL pin. The resistor RF shown in

MPC9774 must have a resistance of 9-10Ω (VCC = 2.5V) to

meet the voltage drop criteria.

The minimum values for RF and the filter capacitor CF are

defined by the required filter characteristics: the RC filter

should provide an attenuation greater than 40 dB for noise

whose spectral content is above 100 kHz. In the example RC

filter shown in MPC9774, the filter cut-off frequency is around

3-5 kHz and the noise attenuation at 100 kHz is better than

42 dB.

RF = 9–10Ω

CF = 22 µF

RF

VCC

VCC_PLL

CF 10 nF MPC9774

33...100 nF

VCC

Figure 10. VCC Power Supply Filter

As the noise frequency crosses the series resonant point

of an individual capacitor its overall impedance begins to look

inductive and thus increases with increasing frequency. The

parallel capacitor combination shown ensures that a low

impedance path to ground exists for frequencies well above

the bandwidth of the PLL. Although the MPC9774 has

several design features to minimize the susceptibility to

power supply noise (isolated power and grounds and fully

differential PLL) there still may be applications in which

overall performance is being degraded due to system power

supply noise. The power supply filter schemes discussed in

this section should be adequate to eliminate power supply

noise related problems in most designs.

Pulse

Generator

Z = 50W

Z = 50Ω

MPC9774 DUT

RT = 50Ω

VTT

Z = 50Ω

RT = 50Ω

VTT

Figure 11. CCLK MPC9774 AC test reference for Vcc = 3.3V and Vcc = 2.5V

TIMING SOLUTIONS

11

MOTOROLA

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet MPC9774.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MPC9772 | 3.3V 1:12 LVCMOS PLL Clock Generator | IDT |

| MPC9772 | 3.3V 1:12 LVCMOS PLL Clock Generator | Motorola Semiconductors |

| MPC9773 | 3.3 V 1:12 LVCMOS PLL Clock Generator | Freescale Semiconductor |

| MPC9774 | LVCMOS PLL CLOCK GENERATOR | Motorola Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |