|

|

PDF ADDI7013 Data sheet ( Hoja de datos )

| Número de pieza | ADDI7013 | |

| Descripción | Dual-Channel CCD Signal Processor | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADDI7013 (archivo pdf) en la parte inferior de esta página. Total 3 Páginas | ||

|

No Preview Available !

Data Sheet

Dual-Channel CCD Signal Processor with

Precision Timing Core

ADDI7013

FEATURES

Differential analog inputs

CDS or SHA (CDS bypass) with 7 gain settings

0 dB to 36 dB, 10-bit variable gain amplifier (VGA)

16-bit, 75 MSPS analog-to-digital converter (ADC)

Precision Timing core with 210 ps resolution at 75 MHz

8 independent H-clock phases with programmable drive

strength (3.6 V maximum swing)

4 general-purpose outputs (GPO)

On-chip sync generator with external sync input

Reduced range LVDS outputs with single clock lane

6 mm × 6 mm CSP_BGA package with 0.5 mm pitch

APPLICATIONS

Industrial cameras

Surveillance cameras

Medical imaging

Professional photography

GENERAL DESCRIPTION

The ADDI7013 is a highly integrated, dual-channel, CCD signal

processor for high speed digital imaging applications. Each channel

is specified at pixel rates of up to 75 MHz and consists of a complete

analog front end (AFE) with analog-to-digital conversion. The

Precision Timing® core allows adjustment of the correlated double

sampler (CDS) and horizontal clocks with 210 ps resolution at

75 MHz operation. There are eight independent horizontal clock

outputs with programmable drive strength to support a variety

of CCD timing requirements.

Each analog front end includes black level clamping; a CDS;

a VGA; and a 16-bit, 75 MSPS analog-to-digital converter (ADC).

Operation is programmed using a 3-wire serial interface.

Packaged in a space-saving, 6 mm × 6 mm, CSP_BGA, the

ADDI7013 is specified over an operating temperature range of

−40°C to +85°C.

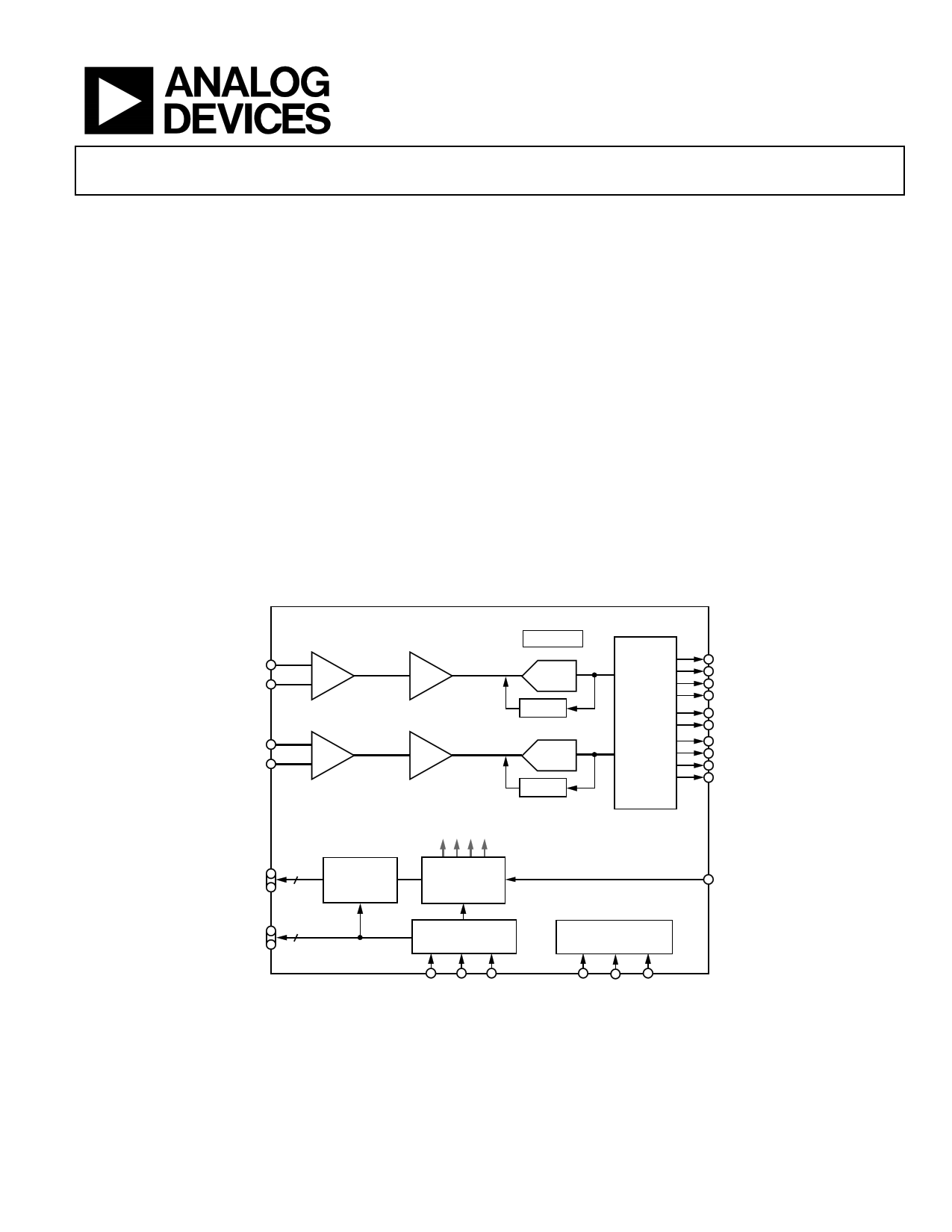

FUNCTIONAL BLOCK DIAGRAM

ADDI7013

VREF

INP_A

INM_A

INP_B

INM_B

CDS/

SHA

0dB TO 18dB

VGA

0dB TO 36dB

ADC

CLAMP

CDS/

SHA

0dB TO 18dB

VGA

0dB TO 36dB

ADC

CLAMP

REDUCED

RANGE

LVDS

INTERFACE

DOUT0P_A

DOUT0N_A

DOUT1P_A

DOUT1N_A

TCLKP

TCLKN

DOUT0P_B

DOUT0N_B

DOUT1P_B

DOUT1N_B

INTERNAL CLOCKS

H1 TO H4

HL1, HL2

RG1, RG2

8

HORIZONTAL

DRIVERS

Precision

Timing

CORE

GPO1 TO GPO4

4

ISATG

INTERNAL

REGISTERS

CLI

HD VD SYNC

Figure 1.

SL SDATA SCK

Rev. Sp0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page | ||

| Páginas | Total 3 Páginas | |

| PDF Descargar | [ Datasheet ADDI7013.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADDI7013 | Dual-Channel CCD Signal Processor | Analog Devices |

| ADDI7015 | 16-Bit CCD Signal Processor | Analog Devices |

| ADDI7018 | 16-Bit HD Image Signal Processor | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |