|

|

PDF AD9748 Data sheet ( Hoja de datos )

| Número de pieza | AD9748 | |

| Descripción | D/A Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9748 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

Data Sheet

8-Bit, 210 MSPS TxDAC® D/A Converter

AD9748

FEATURES

High performance member of pin-compatible

TxDAC product family

Linearity

0.1 LSB DNL

0.1 LSB INL

Twos complement or straight binary data format

Differential current outputs: 2 mA to 20 mA

Power dissipation: 135 mW @ 3.3 V

Power-down mode: 15 mW @ 3.3 V

On-chip 1.20 V reference

CMOS-compatible digital interface

32-lead LFCSP

Edge-triggered latches

Fast settling: 11 ns to 0.1% full-scale

GENERAL DESCRIPTION

The AD97481 is an 8-bit resolution, wideband, third generation

member of the TxDAC series of high performance, low power

CMOS digital-to-analog converters (DACs). The TxDAC

family, consisting of pin-compatible 8-, 10-, 12-, and 14-bit

DACs, is specifically optimized for the transmit signal path of

communication systems. All of the devices share the same

interface options, small outline package, and pinout, providing

an upward or downward component selection path based on

performance, resolution, and cost. The AD9748 offers

exceptional ac and dc performance while supporting update

rates up to 210 MSPS.

The AD9748’s low power dissipation makes it well suited for

portable and low power applications. Its power dissipation can

be further reduced to 60 mW with a slight degradation in

performance by lowering the full-scale current output. In

addition, a power-down mode reduces the standby power

dissipation to approximately 15 mW. A segmented current

source architecture is combined with a proprietary switching

technique to reduce spurious components and enhance

dynamic performance.

APPLICATIONS

Communications

Direct digital synthesis (DSS)

Instrumentation

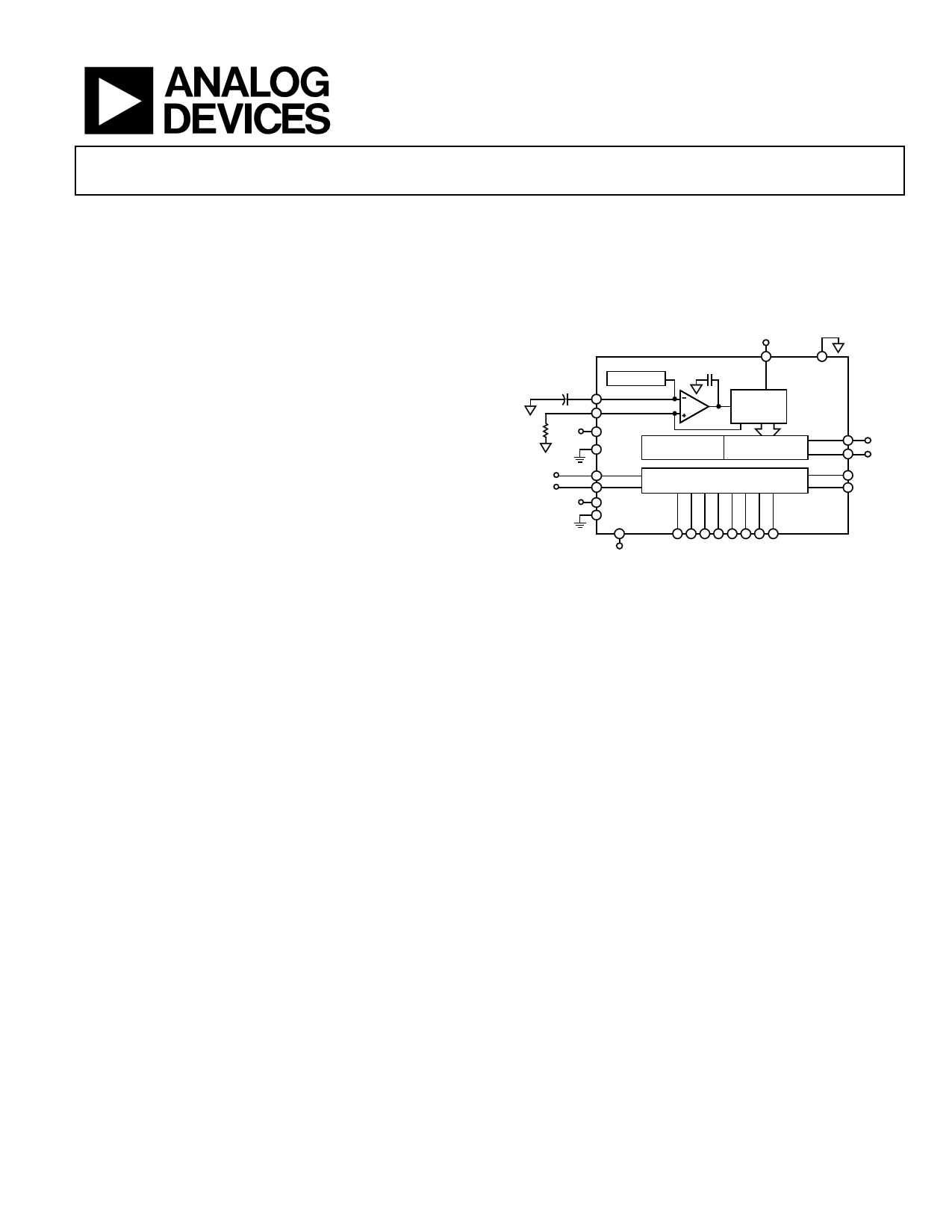

FUNCTIONAL BLOCK DIAGRAM

3.3V

0.1µF

RSET 3.3V

CLK+

CLK–

3.3V

1.2V REF

REFIO

FS ADJ

150pF

DVDD

DCOM

SEGMENTED

SWITCHES

AVDD ACOM

CURRENT AD9748

SOURCE

ARRAY

LSB

SWITCHES

IOUTA

IOUTB

CLKVDD

CLKCOM

LATCHES

MODE

CMODE

DIGITAL DATA INPUTS (DB7–DB0)

SLEEP

Figure 1.

Edge-triggered input latches and a 1.2 V temperature-

compensated band gap reference have been integrated to

provide a complete monolithic DAC solution. The digital inputs

support 3 V CMOS logic families.

PRODUCT HIGHLIGHTS

1. 32-lead LFCSP.

2. The AD9748 is the 8-bit member of the pin-compatible

TxDAC family, which offers excellent INL and DNL

performance.

3. Differential or single-ended clock input (LVPECL or

CMOS), supports 210 MSPS conversion rate.

4. Data input supports twos complement or straight binary

data coding.

5. Low power: Complete CMOS DAC function operates on

135 mW from a 2.7 V to 3.6 V single supply. The DAC full-

scale current can be reduced for lower power operation,

and a sleep mode is provided for low power idle periods.

6. On-chip voltage reference: The AD9748 includes a 1.2 V

temperature-compensated band gap voltage reference.

1 Protected by U.S. Patent Numbers 5568145, 5689257, and 5703519.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2003–2013 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page

AD9748

Data Sheet

DYNAMIC SPECIFICATIONS

TMIN to TMAX, AVDD = 3.3 V, DVDD = 3.3 V, CLKVDD = 3.3 V, IOUTFS = 20 mA, differential transformer coupled output, 50 Ω doubly

terminated, unless otherwise noted.

Table 2.

Parameter

DYNAMIC PERFORMANCE

Maximum Output Update Rate (fCLOCK)

Output Settling Time (tST) (to 0.1%)1

Output Propagation Delay (tPD)

Glitch Impulse

Output Rise Time (10% to 90%)1

Output Fall Time (10% to 90%)1

Output Noise (IOUTFS = 20 mA)2

Output Noise (IOUTFS = 2 mA)2

AC LINEARITY

Signal-to-Noise and Distortion Ratio

fCLOCK = 50 MSPS; fOUT = 5 MHz

fCLOCK = 50 MSPS; fOUT = 19 MHz

fCLOCK = 100 MSPS; fOUT = 5 MHz

fCLOCK = 100 MSPS; fOUT = 39 MHz

fCLOCK = 165 MSPS; fOUT = 5 MHz

fCLOCK = 165 MSPS; fOUT = 49 MHz

fCLOCK = 210 MSPS; fOUT = 9 MHz

fCLOCK = 210 MSPS; fOUT = 68 MHz

Total Harmonic Distortion

fCLOCK = 25 MSPS; fOUT = 1 MHz

fCLOCK = 50 MSPS; fOUT = 12.5 MHz

fCLOCK = 100 MSPS; fOUT = 25 MHz

fCLOCK = 165 MSPS; fOUT = 41.3 MHz

fCLOCK = 210 MSPS; fOUT = 68 MHz

Spurious-Free Dynamic Range to Nyquist

fCLOCK = 25 MSPS; fOUT = 1 MHz

0 dBFS Output

fCLOCK = 65 MSPS; fOUT = 5 MHz

fCLOCK = 65 MSPS; fOUT = 19 MHz

fCLOCK = 100 MSPS; fOUT = 5 MHz

fCLOCK = 100 MSPS; fOUT = 39 MHz

fCLOCK = 165 MSPS; fOUT = 5 MHz

fCLOCK = 165 MSPS; fOUT = 49 MHz

fCLOCK = 210 MSPS; fOUT = 5 MHz

fCLOCK = 210 MSPS; fOUT = 68 MHz

Min Typ Max

210

11

1

5

2.5

2.5

50

30

50

48

50

46

50

47

50

46

−72 −61

−65

−60

−58

−65

61 72

69

65

68

62

68

54

67

60

1 Measured single-ended into 50 Ω load.

2 Output noise is measured with a full-scale output set to 20 mA with no conversion activity. It is a measure of the thermal noise only.

Unit

MSPS

ns

ns

pV-s

ns

ns

pA/√Hz

pA/√Hz

dB

dB

dB

dB

dB

dB

dB

dB

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

dBc

Rev. B | Page 4 of 24

5 Page

AD9748

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

0

fCLOCK = 125MSPS

fOUT = 27MHz

SFDR = 56.2dBc

AMPLITUDE = 0dBFS

10 20 30 40 50 60

FREQUENCY (MHz)

Figure 11. Single-Tone Spectral Plot @ 125 MSPS (Single-Ended Output)

0

–10

fCLOCK = 165MSPS

fOUT = 49MHz

SFDR = 50.1dBc

–20 AMPLITUDE = 0dBFS

–30

–40

–50

–60

–70

–80

–90

–100

0

10 20

30 40 50 60

FREQUENCY (MHz)

70

80

Figure 12. Single-Tone Spectral Plot @ 165 MSPS (Single-Ended Output)

Data Sheet

5ns/DIV

Figure 13. Step Response (Single-Ended Output)

0

–10 fCLOCK = 210MSPS

fOUT = 68MHz

–20 SFDR = 50dBc

AMPLITUDE = 0dBFS

–30

–40

–50

–60

–70

–80

–90

–100

0

10.5

FREQUENCY (MHz)

105

Figure 14. Single-Tone Spectral Plot @ 210 MSPS (Single-Ended Output)

3.3V

0.1µF

RSET 3.3V

CLK+

CLK–

3.3V

1.2V REF

REFIO

FS ADJ

150pF

DVDD

DCOM

SEGMENTED

SWITCHES

AVDD ACOM

CURRENT AD9748

SOURCE

ARRAY

LSB

SWITCHES

CLKVDD

CLKCOM

LATCHES

VDIFF = VOUTA = VOUTB

IOUTA

IOUTB

MODE

CMODE

RLOAD

50Ω

RLOAD

50Ω

DIGITAL DATA INPUTS (DB7–DB0)

SLEEP

Figure 15. Simplified Block Diagram

Rev. B | Page 10 of 24

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet AD9748.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD974 | 4-Channel/ 16-Bit/ 200 kSPS Data Acquisition System | Analog Devices |

| AD9740 | TxDAC D/A Converter | Analog Devices |

| AD9741 | 250 MSPS Digital-to-Analog Converters | Analog Devices |

| AD9742 | TxDAC Digital-to-Analog Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |