|

|

PDF AD9268 Data sheet ( Hoja de datos )

| Número de pieza | AD9268 | |

| Descripción | 1.8V Dual Analog-to-Digital Converter | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9268 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

16-Bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V Dual

Analog-to-Digital Converter (ADC)

AD9268

FEATURES

SNR = 78.2 dBFS @ 70 MHz and 125 MSPS

SFDR = 88 dBc @ 70 MHz and 125 MSPS

Low power: 750 mW @ 125 MSPS

1.8 V analog supply operation

1.8 V CMOS or LVDS output supply

Integer 1-to-8 input clock divider

IF sampling frequencies to 300 MHz

−153.6 dBm/Hz small-signal input noise with 200 Ω input

impedance @ 70 MHz and 125 MSPS

Optional on-chip dither

Programmable internal ADC voltage reference

Integrated ADC sample-and-hold inputs

Flexible analog input range: 1 V p-p to 2 V p-p

Differential analog inputs with 650 MHz bandwidth

ADC clock duty cycle stabilizer

95 dB channel isolation/crosstalk

Serial port control

User-configurable, built-in self-test (BIST) capability

Energy-saving power-down modes

APPLICATIONS

Communications

Diversity radio systems

Multimode digital receivers (3G)

GSM, EDGE, W-CDMA, LTE,

CDMA2000, WiMAX, TD-SCDMA

I/Q demodulation systems

Smart antenna systems

General-purpose software radios

Broadband data applications

Ultrasound equipment

FUNCTIONAL BLOCK DIAGRAM

AVDD

SDIO/ SCLK/

DCS DFS CSB

DRVDD

AD9268

SPI

VIN+A

VIN–A

ADC

PROGRAMMING DATA

CMOS/LVDS 16

OUTPUT BUFFER

ORA

D15A (MSB)

TO

D0A (LSB)

VREF

SENSE

VCM

RBIAS

VIN–B

VIN+B

REF

SELECT

ADC

MULTICHIP

SYNC

DIVIDE 1

TO 8

DUTY CYCLE

DCO

STABILIZER GENERATION

CMOS/LVDS 16

OUTPUT BUFFER

CLK+

CLK–

DCOA

DCOB

ORB

D15B (MSB)

TO

D0B (LSB)

AGND SYNC

PDWN

OEB

NOTES

1. PIN NAMES ARE FOR THE CMOS PIN CONFIGURATION ONLY;

SEE FIGURE 7 FOR LVDS PIN NAMES.

Figure 1.

PRODUCT HIGHLIGHTS

1. On-chip dither option for improved SFDR performance

with low power analog input.

2. Proprietary differential input that maintains excellent SNR

performance for input frequencies up to 300 MHz.

3. Operation from a single 1.8 V supply and a separate digital

output driver supply accommodating 1.8 V CMOS or

LVDS outputs.

4. Standard serial port interface (SPI) that supports various

product features and functions, such as data formatting

(offset binary, twos complement, or gray coding), enabling

the clock DCS, power-down, test modes, and voltage

reference mode.

5. Pin compatibility with the AD9258, allowing a simple

migration from 16 bits to 14 bits. The AD9268 is also pin

compatible with the AD9251, AD9231, and AD9204 family

of products for lower sample rate, low power applications.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2009 Analog Devices, Inc. All rights reserved.

1 page

AD9268

SPECIFICATIONS

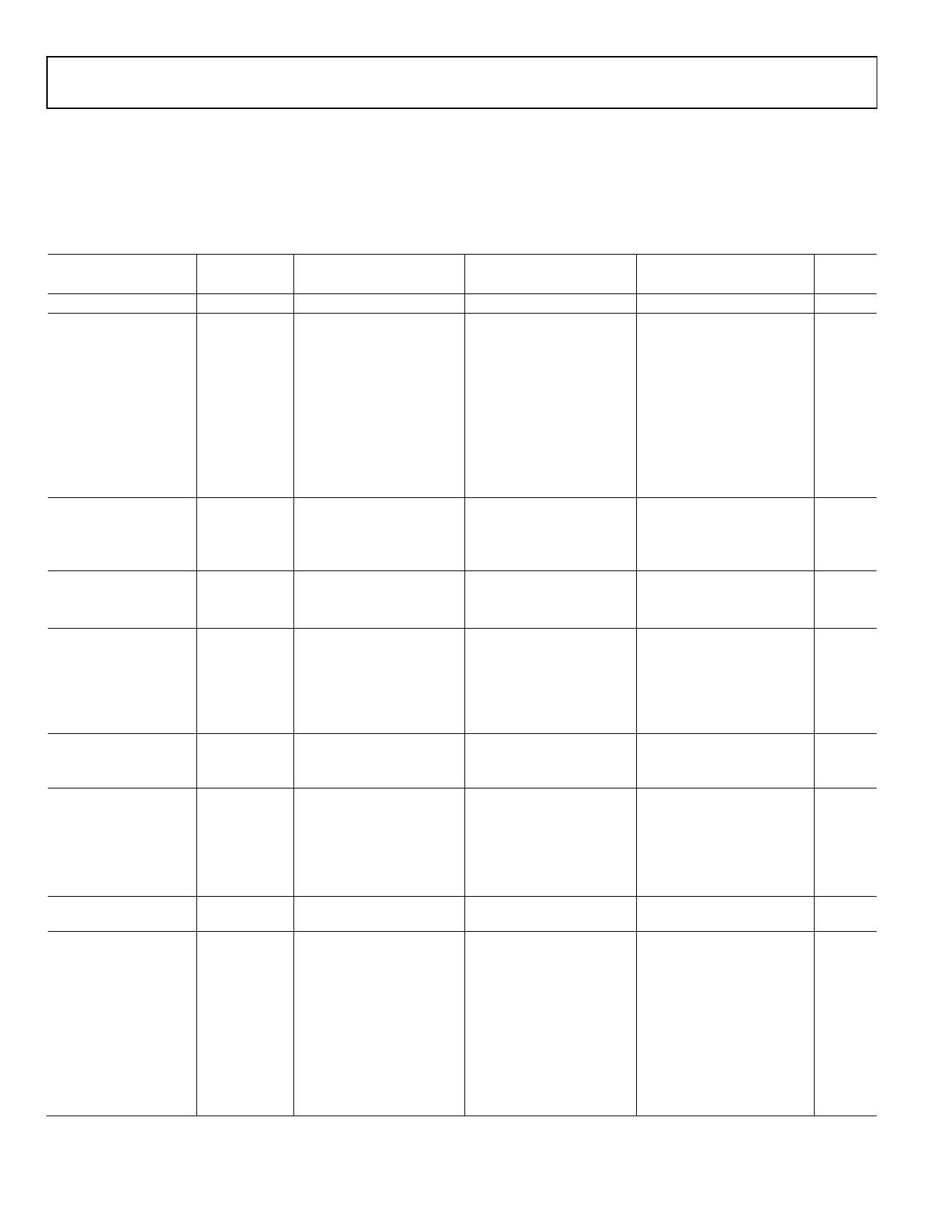

ADC DC SPECIFICATIONS

AVDD = 1.8 V, DRVDD = 1.8 V, maximum sample rate, VIN = −1.0 dBFS differential input, 1.0 V internal reference, DCS enabled, unless

otherwise noted.

Table 1.

Parameter

RESOLUTION

ACCURACY

No Missing Codes

Offset Error

Gain Error

Differential

Nonlinearity (DNL)1

Integral Nonlinearity

(INL)1

MATCHING

CHARACTERISTIC

Offset Error

Gain Error

TEMPERATURE DRIFT

Offset Error

Gain Error

INTERNAL VOLTAGE

REFERENCE

Output Voltage Error

(1 V Mode)

Load Regulation @

1.0 mA

INPUT REFERRED NOISE

VREF = 1.0 V

ANALOG INPUT

Input Span, VREF =

1.0 V

Input Capacitance2

Input Common-

Mode Voltage

REFERENCE INPUT

RESISTANCE

POWER SUPPLIES

Supply Voltage

AVDD

DRVDD

Supply Current

IAVDD1

IDRVDD1 (1.8 V

CMOS)

IDRVDD1 (1.8 V

LVDS)

Temperature

Full

Full

Full

Full

Full

25°C

Full

25°C

Full

Full

Full

Full

Full

Full

25°C

Full

Full

Full

Full

Full

Full

Full

Full

Full

AD9268BCPZ-80

Min Typ

Max

16

Guaranteed

±0.2 ±0.4

±0.4 ±2.5

−1.0 +1.4

±0.65

±4.5

±2.0

±0.1 ±0.4

±0.3 ±1.3

±2

±15

±5 ±12

5

2.17

2

8

0.9

6

1.7 1.8

1.7 1.8

234

35

89

1.9

1.9

240

AD9268BCPZ-105

Min Typ

Max

16

Guaranteed

±0.2 ±0.5

±0.4 ±2.5

−1.0 +1.3

±0.7

±5.1

±3.0

±0.1 ±0.4

±0.3 ±1.3

±2

±15

±5 ±12

5

2.23

2

8

0.9

6

1.7 1.8

1.7 1.8

293

45

89

1.9

1.9

300

AD9268BCPZ-125

Min Typ

Max

16

Guaranteed

±0.4 ±0.65

±0.4 ±2.5

−1.0 +1.2

±0.7

±5.5

±3.0

±0.2 ±0.45

±0.3 ±1.3

±2

±15

±5 ±12

5

2.27

2

8

0.9

6

1.7 1.8

1.7 1.8

390

55

94

1.9

1.9

400

Unit

Bits

% FSR

% FSR

LSB

LSB

LSB

LSB

% FSR

% FSR

ppm/°C

ppm/°C

mV

mV

LSB

rms

V p-p

pF

V

kΩ

V

V

mA

mA

mA

Rev. A | Page 4 of 44

5 Page

AD9268

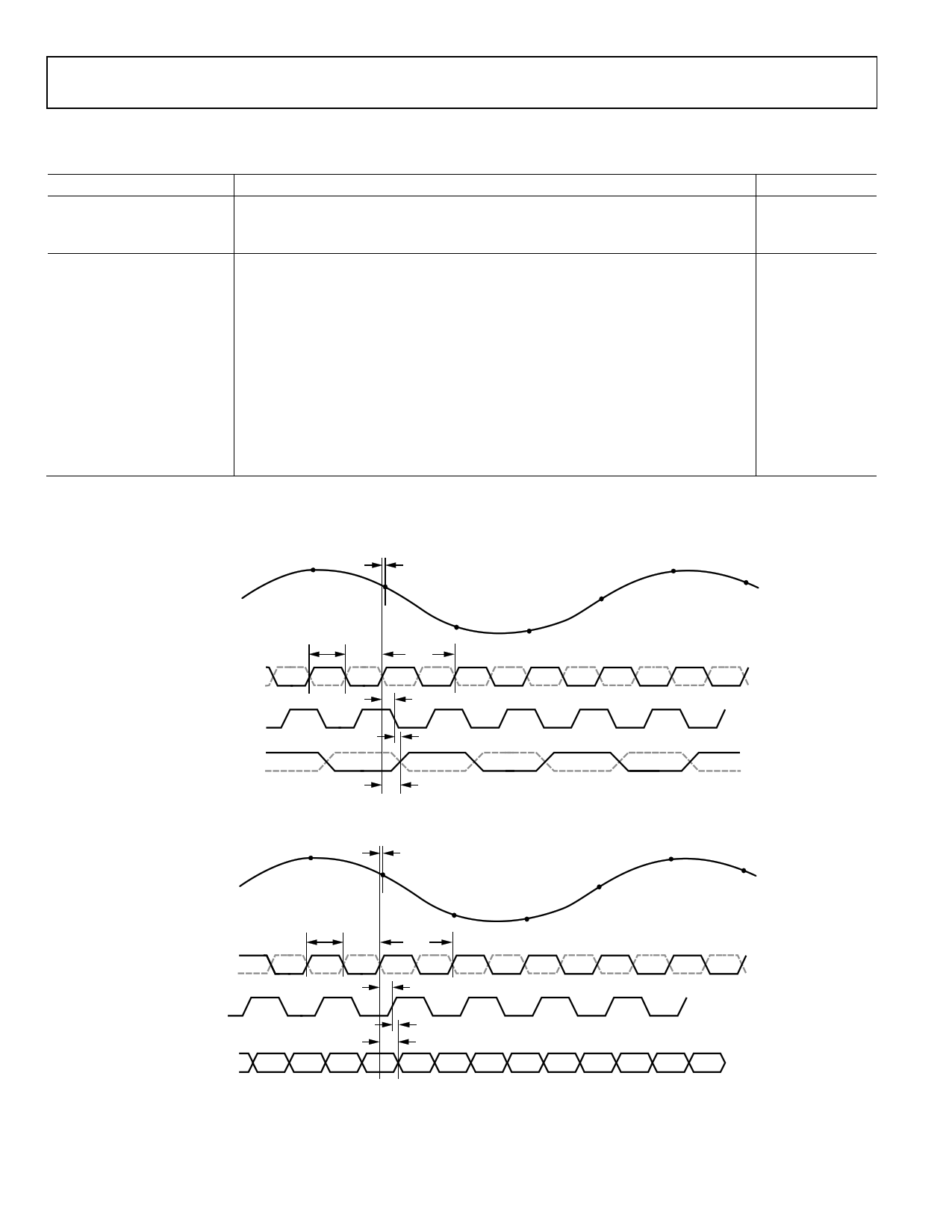

TIMING SPECIFICATIONS

Table 5.

Parameter

SYNC TIMING REQUIREMENTS

tSSYNC

tHSYNC

SPI TIMING REQUIREMENTS

tDS

tDH

tCLK

tS

tH

tHIGH

tLOW

tEN_SDIO

tDIS_SDIO

Conditions

SYNC to rising edge of CLK+ setup time

SYNC to rising edge of CLK+ hold time

Setup time between the data and the rising edge of SCLK

Hold time between the data and the rising edge of SCLK

Period of the SCLK

Setup time between CSB and SCLK

Hold time between CSB and SCLK

SCLK pulse width high

SCLK pulse width low

Time required for the SDIO pin to switch from an input to an output relative to the SCLK

falling edge

Time required for the SDIO pin to switch from an output to an input relative to the SCLK

rising edge

Limit

0.3 ns typ

0.40 ns typ

2 ns min

2 ns min

40 ns min

2 ns min

2 ns min

10 ns min

10 ns min

10 ns min

10 ns min

Timing Diagrams

VIN

CLK+

CLK–

DCOA/DCOB

CH A/CH B DATA

VIN

CLK+

CLK–

DCOA/DCOB

CH A/CH B DATA

N–1

tCH

tA

N

N+1

tCLK

N+2

N+3

N+4

N+5

tDCO

tSKEW

N – 13

N – 12

N – 11

N – 10

tPD

Figure 2. CMOS Default Output Mode Data Output Timing

N–9

N–8

N–1

tCH

tA

N

N+1

tCLK

N+2

N+3

N+4

N+5

tDCO

tSKEW

tPD

CH A CH B CH A CH B CH A CH B

N – 12 N – 12 N – 11 N – 11 N – 10 N – 10

CH A

N–9

CH B

N–9

CH A

N–8

Figure 3. CMOS Interleaved Output Mode Data Output Timing

Rev. A | Page 10 of 44

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9268.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9260 | High Speed Oversampling CMOS ADC | Analog Devices |

| AD9261 | 30 MSPS to 160 MSPS Continuous Time Sigma-Delta ADC | Analog Devices |

| AD9262 | 30 MSPS to 160 MSPS Dual Continuous Time Sigma-Delta ADC | Analog Devices |

| AD9265 | 1.8V Analog-to-Digital Converter | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |