|

|

PDF 82P33813 Data sheet ( Hoja de datos )

| Número de pieza | 82P33813 | |

| Descripción | Synchronization Management Unit | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 82P33813 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

Synchronization Management Unit for

IEEE 1588 and synchronous Ethernet

82P33813

Short Form Datasheet

This is a short form datasheet and is intended to provide an overview only. Additional details are available from IDT. Contact information may be found on

the last page.

HIGHLIGHTS

• Synchronization Management Unit (SMU) provides tools to manage

physical layer and packet based synchronous clocks for IEEE 1588 /

PTP Telecom Profile applications

• Supports independent IEEE 1588 and Synchronous Ethernet

(SyncE) timing paths

• Combo mode provides SyncE physical layer frequency support for

IEEE 1588 Telecom Boundary Clock (T-BC) and Telecom Time Slave

Clocks (T-TSC) per G.8273.2

• Digital PLL 1 (DPLL1) and DPLL 2 can be configured as Digitally

Controlled Oscillators (DCOs) for PTP clock synthesis

• DCO frequency resolution is [(77760 / 1638400) * 2^-48] or

~1.686305041e-10 ppm

• DPLL1 and DPLL2 generate G.8262 compliant SyncE clocks

• Two independent Time of Day (ToD) counters/time accumulators, one

associated with each of DPLL1 and DPLL2, can be used to track dif-

ferences between the two time domains and to time-stamp external

events

• DPLL3 performs rate conversions to frequency synchronization inter-

faces or for other general purpose timing applications

• APLL generates clocks with jitter < 1 ps RMS (12 kHz to 20 MHz) for:

1000BASE-T and 1000BASE-X

• Fractional-N input dividers support a wide range of reference fre-

quencies

• Locks to 1 Pulse Per Second (PPS) references

• It can be configured from an external EEPROM after reset

FEATURES

• Differential reference inputs (IN1 to IN4) accept clock frequencies

between 1 PPS and 650 MHz

• Single ended inputs (IN5 to IN6) accept reference clock frequencies

between 1 PPS and 162.5 MHz

• Loss of Signal (LOS) pins (LOS0 to LOS3) can be assigned to any

clock reference input

• Reference monitors qualify/disqualify references depending on activ-

ity, frequency and LOS pins

• Automatic reference selection state machines select the active refer-

ence for each DPLL based on the reference monitors, priority tables,

revertive and non-revertive settings and other programmable settings

• Fractional-N input dividers enable the DPLLs to lock to a wide range

of reference clock frequencies including: 10/100/1000 Ethernet, 10G

Ethernet, OTN, SONET/SDH, PDH, TDM, GSM, CPRI and GNSS

frequencies

• Any reference input (IN1 to IN6) can be designated as external sync

pulse inputs (1 PPS, 2 kHz, 4 kHz or 8 kHz) associated with a select-

able reference clock input

• FRSYNC_8K_1PPS and MFRSYNC_2K_1PPS output sync pulses

that are aligned with the selected external input sync pulse input and

frequency locked to the associated reference clock input

• DPLL1 and DPLL2 can be configured with bandwidths between 0.09

mHz and 567 Hz

• DPLL1 and DPLL2 lock to input references with frequencies between

1 PPS and 650 MHz

• DPLL3 locks to input references with frequencies between 8 kHz and

650 MHz

• DPLL1 and DPLL2 comply with ITU-T G.8262 for Synchronous

Ethernet Equipment Clock (EEC), and G.813 for Synchronous Equip-

ment Clock (SEC); and Telcordia GR-253-CORE for Stratum 3 and

SONET Minimum Clock (SMC)

• DPLL1 and DPLL2 generate clocks with PDH, TDM, GSM, CPRI/

OBSAI, 10/100/1000 Ethernet and GNSS frequencies; these clocks

are directly available on OUT1 and OUT5

• DPLL3 generates N x 8 kHz clocks up to 100 MHz that are output on

OUT6 and OUT7

• DPLL1 and DPLL2 can be configured as DCOs to synthesize IEEE

1588 clocks

• APLL can be connected to DPLL1 or DPLL2

• APLL generates 10/100/1000 Ethernet, 10G Ethernet, or SONET/

SDH frequencies

• Any of eight common TCXO/OCXO frequencies can be used for the

System Clock: 10 MHz, 12.8 MHz, 13 MHz, 19.44 MHz, 20 MHz,

24.576 MHz, 25 MHz or 30.72 MHz

• The I2C slave, SPI or the UART interface can be used by a host pro-

cessor to access the control and status registers

• The I2C master interface can automatically load a device configura-

tion from an external EEPROM after reset

• Differential outputs OUT3 and OUT4 output clocks with frequencies

between 1 PPS and 650 MHz

• Single ended outputs OUT1, OUT2 and OUT5 output clocks with fre-

quencies between 1 PPS and 125 MHz

• DPLL1 and DPLL2 support independent programmable delays for

each of IN1 to IN6; the delay for each input is programmable in steps

of 0.61 ns with a range of ~±78 ns

• The input to output phase delay of DPLL1 and DPLL2 is programma-

ble in steps of 0.0745 ps with a total range of ±20 μs

• The clock phase of each of the output dividers for OUT1 (from APLL)

to OUT4 is individually programmable in steps of ~200 ps with a total

range of +/-180°

• 1149.1 JTAG Boundary Scan

• 72-pin QFN green package

APPLICATIONS

• Access routers, edge routers, core routers

• Carrier Ethernet switches

• Multiservice access platforms

• Optical network terminal (ONT)

• Distribution point Unit (DPU)

• PON OLT

• LTE eNodeB

• IEEE 1588 / PTP Telecom Profile clock synthesizer

• ITU-T G.8273.2 Telecom Time Slave Clock (T-TSC)

• ITU-T G.8264 Synchronous Equipment Timing Source (SETS)

• ITU-T G.8263 Packet-based Equipment Clock (PEC)

• ITU-T G.8262 Synchronous Ethernet Equipment Clock (EEC)

• ITU-T G.813 Synchronous Equipment Clock (SEC)

• Telcordia GR-253-CORE Stratum 3 Clock (S3) and SONET Minimum

Clock (SMC)

©2016 Integrated Device Technology, Inc.

1

March 16, 2016

1 page

82P33813 Short Form Datasheet

2 PIN DESCRIPTION

Table 1: Pin Description

Pin No.

6

58

59

52

7

8

9

31

32

33

34

35

36

38

39

37

41

43

44

Name

OSCI

MS/SL

SONET/SDH/

LOS3

RSTB

XO_FREQ0/

LOS0

XO_FREQ1/

LOS1

XO_FREQ2/

LOS2

IN1_POS

IN1_NEG

IN2_POS

IN2_NEG

IN3_POS

IN3_NEG

IN4_POS

IN4_NEG

IN5

IN6

FRSYNC

_8K_1PPS

MFRSYNC

_2K_1PPS

I/O Type

Description

Global Control Signal

OSCI: Crystal Oscillator System Clock

I CMOS A clock provided by a crystal oscillator is input on this pin. It is the system clock for the

device. The oscillator frequency is selected via pins XO_FREQ0 ~ XO_FREQ2

I

pull-up

I

pull-down

I

pull-up

CMOS

CMOS

CMOS

MS/SL: Master / Slave Selection

This pin, together with the MS_SL_CTRL bit, controls whether the device is configured as the

Master or as the Slave. The signal level on this pin is reflected by the MASTER_SLAVE bit.

SONET/SDH: SONET / SDH Frequency Selection

During reset, this pin determines the default value of the IN_SONET_SDH bit:

High: The default value of the IN_SONET_SDH bit is ‘1’ (SONET);

Low: The default value of the IN_SONET_SDH bit is ‘0’ (SDH).

After reset, the value on this pin takes no effect.

LOS3- This pin is used to disqualify input clocks.

RSTB: Reset

I

pull-down

CMOS

XO_FREQ0 ~ XO_FREQ2: These pins set the oscillator frequency.

XO_FREQ[2:0] Oscillator Frequency (MHz)

000 10.000

001 12.800

010 13.000

011 19.440

100 20.000

101 24.576

110 25.000

111 30.720

LOS0 ~ LOS2 - These pins are used to disqualify input clocks. After reset, this pin takes on

the operation of LOS0-LOS2

Input Clock and Frame Synchronization Input Signal

IN1_POS / IN1_NEG: Positive / Negative Input Clock 1

I PECL/LVDS A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

IN2_POS / IN2_NEG: Positive / Negative Input Clock 1

I PECL/LVDS A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

IN3_POS / IN3_NEG: Positive / Negative Input Clock 3

I PECL/LVDS A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

IN4_POS / IN4_NEG: Positive / Negative Input Clock 4

I PECL/LVDS A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

I

pull-down

CMOS

IN5: Input Clock 5

A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

I

pull-down

CMOS

IN6: Input Clock 6

A reference clock is input on this pin.This pin can also be used as a sync input, and in this

case a 2 kHz, 4 kHz, 8 kHz, or 1PPS signal can be input on this pin.

Output Frame Synchronization Signal

O

CMOS

FRSYNC_8K_1PPS: 8 kHz Frame Sync Output

An 8 kHz signal or a 1PPS sync signal is output on this pin.

O

CMOS

MFRSYNC_2K_1PPS: 2 kHz Multiframe Sync Output

A 2 kHz signal or a 1PPS sync signal is output on this pin.

©2016 Integrated Device Technology, Inc.

5

March 16, 2016

5 Page

82P33813 Short Form Datasheet

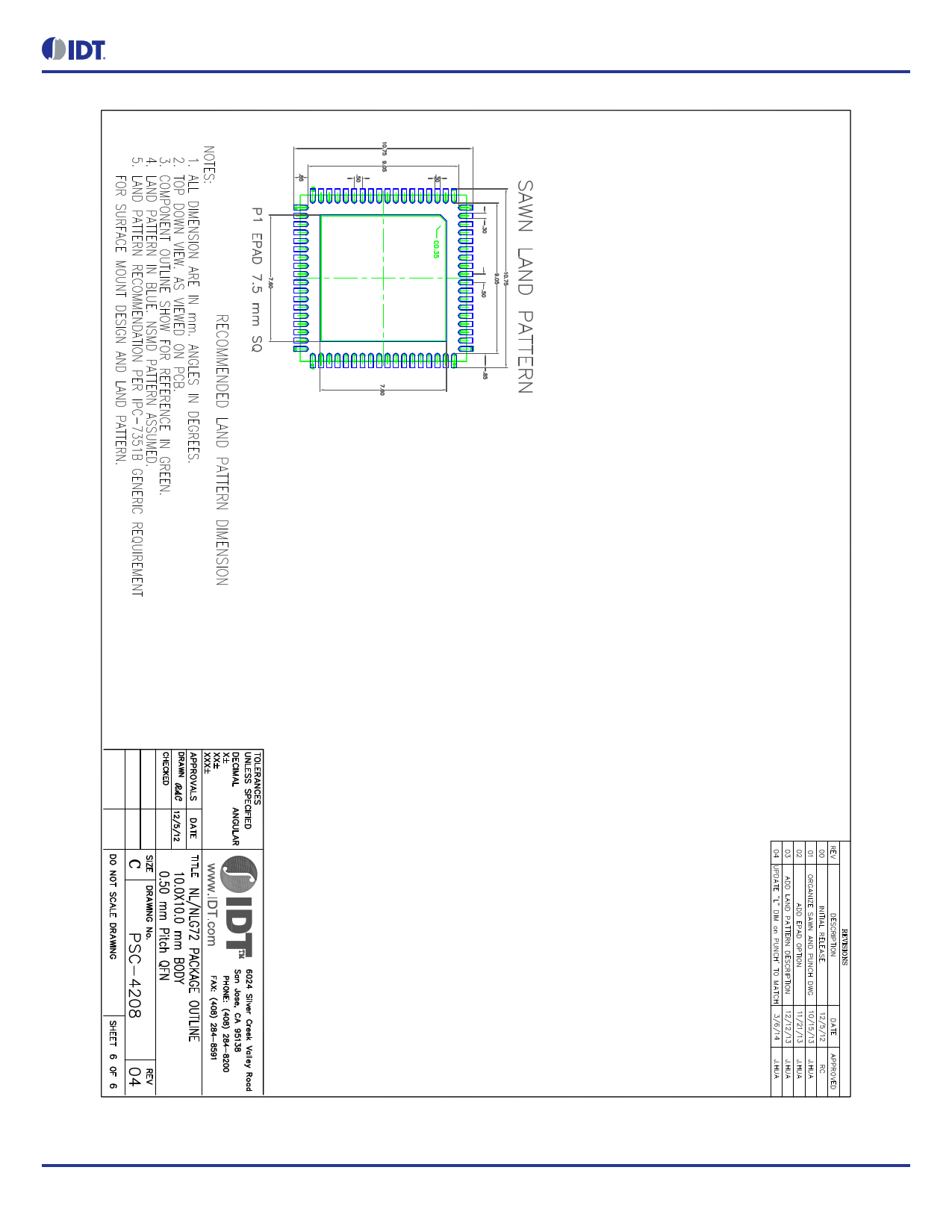

Figure 5. 72-Pin QFN Package Recommended Land Pattern

©2016 Integrated Device Technology, Inc.

11

March 16, 2016

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet 82P33813.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 82P33810 | Synchronization Management Unit | Integrated Device Technology |

| 82P33813 | Synchronization Management Unit | Integrated Device Technology |

| 82P33814 | Synchronization Management Unit | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |