|

|

PDF NB3N4666C Data sheet ( Hoja de datos )

| Número de pieza | NB3N4666C | |

| Descripción | 3.3 V Quad LVCMOS Differential Line Receiver Translator | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3N4666C (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

NB3N4666C

3.3 V Quad LVCMOS

Differential Line Receiver

Translator

Description

The NB3N4666C is a quad−channel LVDS line receiver/translator

offering data rates up to 400 Mbps (200 MHz) and low power

consumption. The NB3N4666C receiver incorporates input fail−safe

protection circuit that provides a known output voltage under input

open−circuit, short and terminated (100 W) conditions. The four

independent inputs accept differential signals such as: M−LVDS,

LVDS, LVPECL and HCSL and translates them to a single−ended,

3.3 V LVCMOS.

The NB3N4666C also offers active high and active low

enable/disable inputs (EN and EN) that allow users to control outputs

of all four receivers. These inputs enable or disable the receivers and

switch the outputs to an active or high impedance state respectively

(see Table 2). The high impedance mode feature helps to reduce the

quiescent power consumption to less than 10 mW typical, when the

outputs of one or more NB3N4666C devices are multiplexed together.

Features

• Accepts M−LVDS, LVDS, LVPECL and HCSL Differential Input

Signal Levels

• Maximum Data Rate of 400 Mbps

• Maximum Clock Frequency of 200 MHz

• 25 ps Typical Channel−to−Channel Skew

• 3.3 ns Maximum Propagation Delay

• 3.3 V ±10% Power Supply

• High Impedance Outputs When Disabled

♦ Low Quiescent Power < 10 mW Typical

• Supports Open, Short, and Terminated Input Fail−safe

• −40°C to +85°C Ambient Operating Temperature

• 16−Pin TSSOP, 5.0 mm x 4.4 mm x 1.2 mm

• These are Pb−Free Devices

Applications

• Point−to−point Data Transmission

• Backplane Receivers

• Clock Distribution Networks

• Multidrop Buses

www.onsemi.com

1

TSSOP−16

DT SUFFIX

CASE 948F

MARKING

DIAGRAMS

16

NB3N

4666

ALYWG

G

1

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

IN1

IN1

OUT1

EN

NB3N4666C

R1 R4

VCC

IN4

IN4

OUT4

EN

OUT2

OUT3

R2 R3

IN2

IN2

GND

IN3

IN3

Figure 1. Functional Block Diagram

ORDERING INFORMATION

See detailed ordering and shipping information on page 8 of

this data sheet.

© Semiconductor Components Industries, LLC, 2016

April, 2016 − Rev. 0

1

Publication Order Number:

NB3N4666C/D

1 page

NB3N4666C

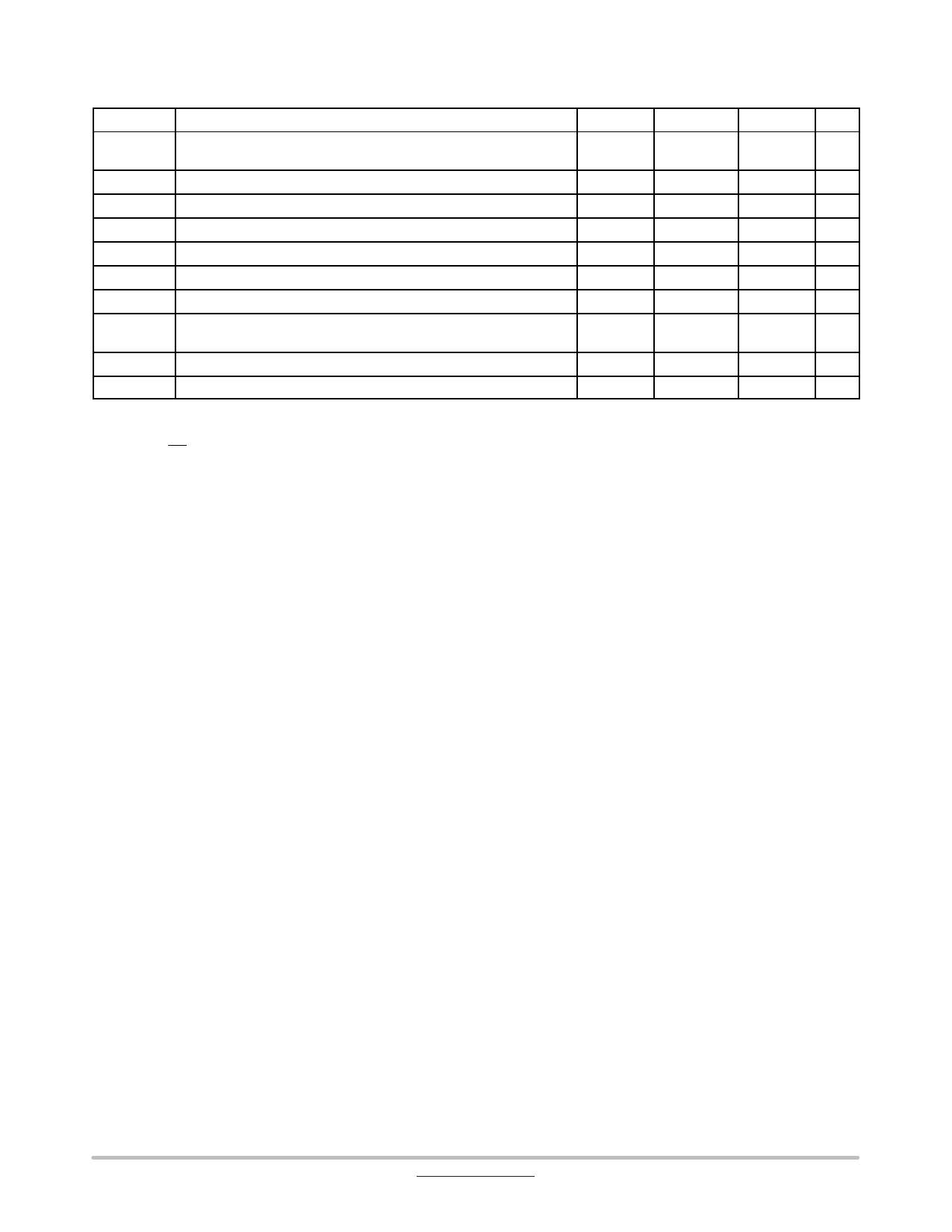

Table 6. AC CHARACTERISTICS (VCC = 3.3 V ± 10%; TA = −40°C to +85°C) (Note 7)

Symbol

Characteristic

Min Typ Max Unit

fMAX

Maximum Input Clock Frequency (Note 8)

All Channels Switching

200 250

MHz

fDATAMAX Maximum Data Rate

400 Mbps

tplh/tphl

Propagation Delay (Note 9) (Figures 5 and 8)

1.8 3.3 ns

tSKEW(o−o) Channel−to−channel Skew (Note 10)

0 25 250 ps

tSKEW(pp) Part−to−part Skew (Note 11)

50 500 ps

tSKEW(p) Pulse Skew ⎢tPHL−tPLH⏐, VCM = VCC/2 (Note 12) (Figures 5 and 8)

0

50 300 ps

tr/tf Output Rise/Fall Time, 20% − 80% (Figures 5 and 8)

600

1200

ps

Tjit (f)

Additive RMS Phase Jitter

Integration Range: 12 kHz − 20 MHz, fc = 100 MHz, 25°C, VCC = 3.3 V

161

fs

tplz/tphz Output Disable Time (Figures 9 and 10)

RL = 2 kW

10 14 ns

tpzl/tpzh Output Enable Time (Figures 9 and 10)

RL = 2 kW

2 5 ns

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product

performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Generator waveform for all tests, unless otherwise specified: f = 50 MHz, CL = 10 pF (includes jig capacitance), tr and tf (10% to 90%) ≤ 2

ns for INx/INx.

8. fMAX generator input conditions: tr = tf < 1ns (10% to 90%), 50% duty cycle, differential (1.05 V to 1.35 V peak to peak). Output Criteria:

40% − 60% duty cycle, VOL (max 0.4 V), VOH (min 2.7 V), CL = 10 pF (stray plus probes)

9. Measured from the differential crosspoint of the input to VCC/2 of the output.

10. tSKEW(O−O) is defined as skew between outputs of the same device at the same supply voltage and with equal load conditions.

11. tSKEW(pp) is defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions.

Using the same type of inputs on each device, the outputs are measured at the differential cross points.

12. tSKEW(p) is the magnitude difference in the differential propagation delay time between the positive−going edge and the negative−going edge

of the same channel.

www.onsemi.com

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet NB3N4666C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3N4666C | 3.3 V Quad LVCMOS Differential Line Receiver Translator | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |